# PHISIC'2018 – ABSTRACTS

## // KEYNOTE // DEEP LEARNING FOR EMBEDDED SECURITY EVALUATION

## Emmanuel Prouff // ANSSI

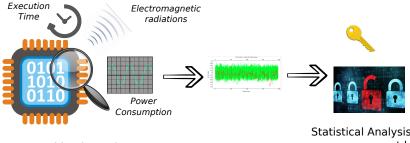

To provide insurance on the resistance of a system against side-channel analysis, several national or private schemes are today promoting an evaluation strategy, common in classical cryptography, which is focusing on the most powerful adversary who may train to learn about the dependency between the device behavior and the sensitive data values. Several works have shown that this kind of analysis, known as Template Attacks in the side-channel domain, can be rephrased as a classical Machine Learning classification problem with learning phase.

Following the current trend in the latter area, recent works have demonstrated that deep learning algorithms were very efficient to conduct security evaluations of embedded systems and had many advantages compared to the other methods. During the proposed presentation, I will come back on these recent works and will identify some avenues for further research on this topic.

# // SESSION // SIDE-CHANNEL ANALYSIS: ATTACKS & PROTECTIONS (I)

## 1. SCATTER: A New DIMENSION IN SIDE-CHANNEL

## <u>Benoit Feix</u> // eSHARD

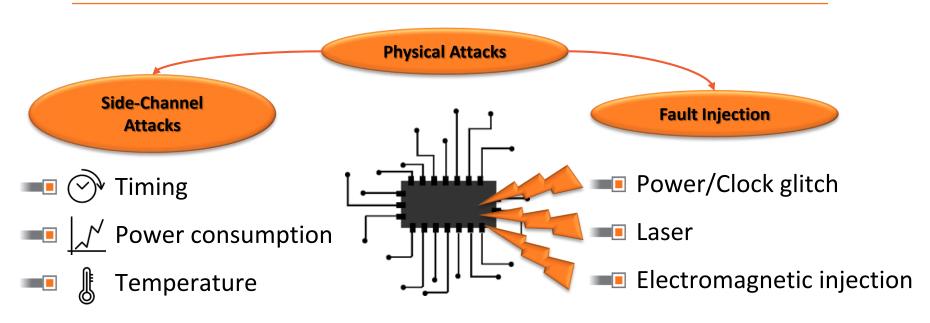

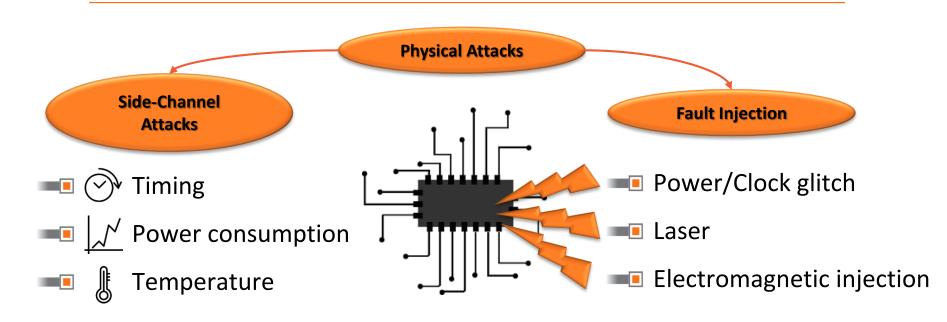

Side-channel techniques have been progressing over the last few years, leading to the creation of a variety of statistical tools, aiming at extracting secrets handled in cryptographic algorithms. In the same time Integrated Circuit manufacturers and final product developers were improving the strength of their countermeasures. In particular their products were facing more and more enhanced attacks during security certifications.

Noticeably, the vast majority of side-channel techniques requires to get the traces aligned together prior to applying statistics. This prerequisite turns out to be challenging in the practical realization of attacks as implementations tend to include hardware or software countermeasures to increase this difficulty. This can be typically achieved by adding random jitters, random clock dividers, or random executions with fake operations, etc.

In this paper, we introduce the new side-channel technique scatter, whose potential is to tackle alignment issues. By construction, scatter brings an additional dimension and opens the door to a large set of potential new attack techniques.

The effectiveness of scatter has been proven on both simulated traces and real world secure products. In summary scatter is a new side-channel technique offering a valuable alternative when the trace alignment represents an issue. Furthermore, scatter represents a suitable option for low-cost attacks, as the requirements in terms of equipment and expertise are significantly reduced.

We will present during our talk the principles of scatter as well as practical results through live demonstrations.

*NB*: from the publication: *SCATTER: A New Dimension in Side-Channel*. Hugues Thiebeauld, Georges Gagnerot, Antoine Wurcker and Christophe Clavier. COSADE 2018. To appear.

## 2. AUTOMATED SOFTWARE PROTECTION FOR THE MASSES AGAINST SIDE-CHANNEL ATTACKS

# <u>Nicolas Belleville</u> // Université Grenoble Alpes, CEA Tech, Damien Courousse, Henri-Pierre Charles // CEA Tech, Karine Heydemann // Sorbonne Universités, LIP6

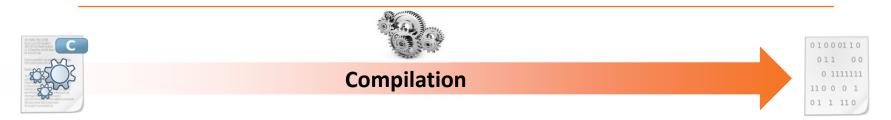

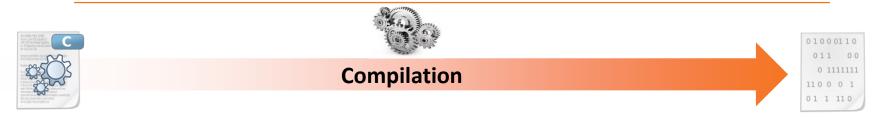

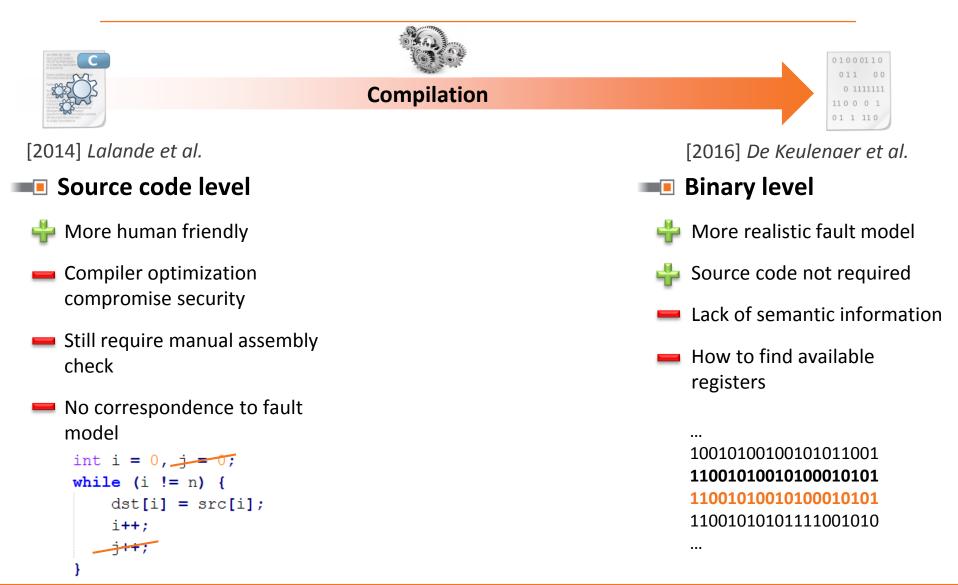

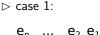

Side-channel attacks represent a major threat for IOT devices and embedded systems. As the number of such devices is currently fastly growing, there is an urgent need for securing them against sidechannel attacks. In this presentation, we will present an automated approach to increase the security of any program against power/EM side channel attacks. The approach is lightweight and can be used with constrained devices. Our approach relies on a combination of static compilation and dynamic code generation in order to make the countermeasure as efficient as possible. The protection is based on code polymorphism, which corresponds to the capability of regularly changing the behaviour of a component at runtime without altering its functional properties. More precisely, several transformations are gathered to make the code vary, such as register shuffling, instruction shuffling, semantic variants and insertion of dummy instructions. The level of security is completely configurable as each transformation can be enabled/disabled, and as some of them provide a tunable level of variability.

In this talk,

- We present how to use compilation to generate specialized runtime generators of polymorphic code, and how the specialization of such generators helps to mitigate some JIT security issues.

- Then, we describe how the runtime generators make the code vary. We discuss the code transformations involved with filtering/resynchronization attacks in mind.

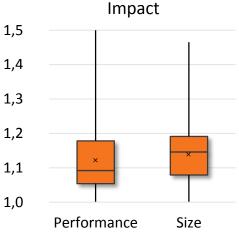

- We give experimental results on security aspects (CPA and t-test) as well as performance aspects for several configurations. We show that one can reach strong security levels using our approach.

# // SESSION // ADVANCED CRYPTOGRAPHIC PRIMITIVES

# 3. FHE AND MPC PRIVACY PRESERVING COMPUTATIONS IN THE CLOUD

# <u>Nicolas Gama</u> // EPFL

In this talk, we briefly introduce *fully homomorphic encryption* (FHE) and *multiparty computations* (MPC), and give an overview of the main constructions, as well as the underlying security assumptions or adversarial models behind these models.

For homomorphic encryption, we explain the original concept introduced by Gentry in 2009 and explain the current state of the art, both in theory (with the underlying Approx-GCD and RingLWE lattice problem), and in practice by introducing a few open source libraries.

For MPC, we briefly present the concept of masking, secret sharing, oblivious transfer and garbled circuits, and illustrate a few examples.

Finally, we compare both approaches, if the final goal is to achieve privacy preserving computations in the cloud.

# 4. STARTING TRANSITION TOWARDS PRODUCTS EMBEDDING POST-QUANTUM CRYPTOGRAPHY

# Yannick Teglia, Aline Gouget // GEMALTO

In 1996, the cryptographers Shorr and Grover separately imagined how a quantum computer could defeat some classical cryptographic algorithms and then proposed procedures to do so. Prototypes of such machines exist today and the digital world giants are pouring a lot of money in this field. This speeds up the need for having intrinsically resistant algorithms as emphasized by the recent NIST initiative.

We will do an overview of where we're standing today in term of threats regarding quantum computing against cryptography. We will also discuss about the current projects, initiatives and technical proposals on Post Quantum Cryptography, in the academic world and in the industrial world as well.

Finally we will discuss about the implications on the implementations and the final products.

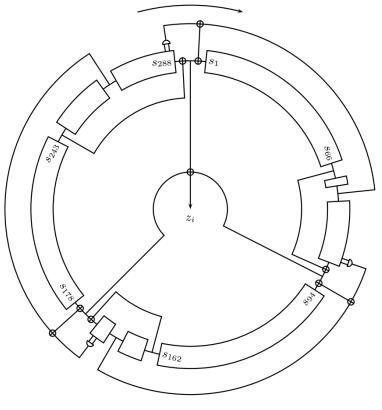

# 5. IMPACT OF FREQUENCY LOCKING ON RING OSCILLATING CELLS IN FPGA

# <u>Ugo Mureddu</u>, Nathalie Bochard, Lilian Bossuet, Viktor Fischer // Univ Lyon, UJM-Saint-Etienne, CNRS, Laboratoire Hubert Curien UMR 5516

Electronic oscillators are key elements in many applications. They are used in most of digital circuits as time reference for synchronizing operations. In the security field, oscillators serve as entropy source for True Random Number Generator (TRNG) or Physical Unclonable Functions (PUF).

Among all the available structures, CMOS ring oscillating cells are particularly interesting in the context of digital Integrated Circuits (IC) since they are fully digital which make them very easy to integrate. However, a phenomena, very little studied and taken into account, that influence CMOS ring oscillating cells is their ability to easily lock a signal with a frequency close to their natural oscillation frequency. Interaction between two oscillatory systems spatially close operating at frequency which are close to each other is a well know effect. This phenomena is called locking.

Although some particular applications like frequency divider are taking advantage of it, in most cases this is something the designers want to avoid. Indeed, locking on ring oscillating cells used for security applications could be very prejudicial. Let's consider a ring oscillating cells based TRNG used to generate encryption keys for secure communication between two people, keys generated from a locked ring oscillating cell will be fully deterministic and thus completely insecure.

This paper presents a complete study of locking phenomena on the main types of CMOS ring oscillating cells: Ring Oscillator (RO), Transient Effect Ring Oscillator (TERO) and Self Time Ring (STR).

First of all, to the best of our knowledge, it is demonstrated for the first time that locking is affecting specific configurations of ring oscillating cells like TERO and STR. Moreover, while some work has been done on the influence of locking on classical RO, there is at the moment no exhaustive evaluation. That's why, a full study of locking phenomena on different FPGA families is carried. The advantage of carrying this study on FPGA instead of dedicated IC is double. First, it permits to enlarge the scope of experimentation by reconfiguring the FPGAs. Then, the oscillations frequency of studied cells in FPGA is lower than in ASIC and allow us to output them on measurement devices. The three main FPGA families, namely Xilinx, Intel (SRAM based FPGA) and Microsemi (FLASH based FPGA), are targeted in this work.

# // SESSION // FAULT INJECTION ANALYSIS: ATTACKS AND PROTECTIONS (I)

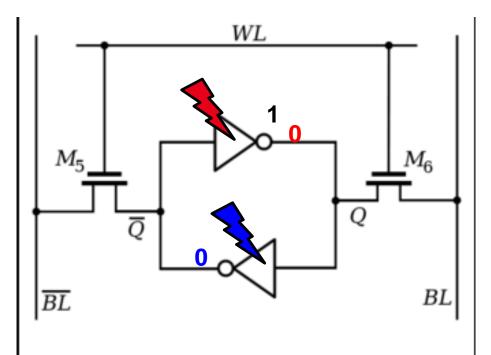

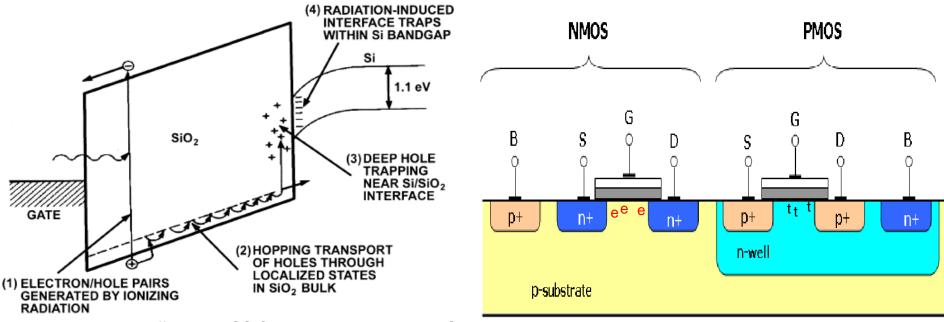

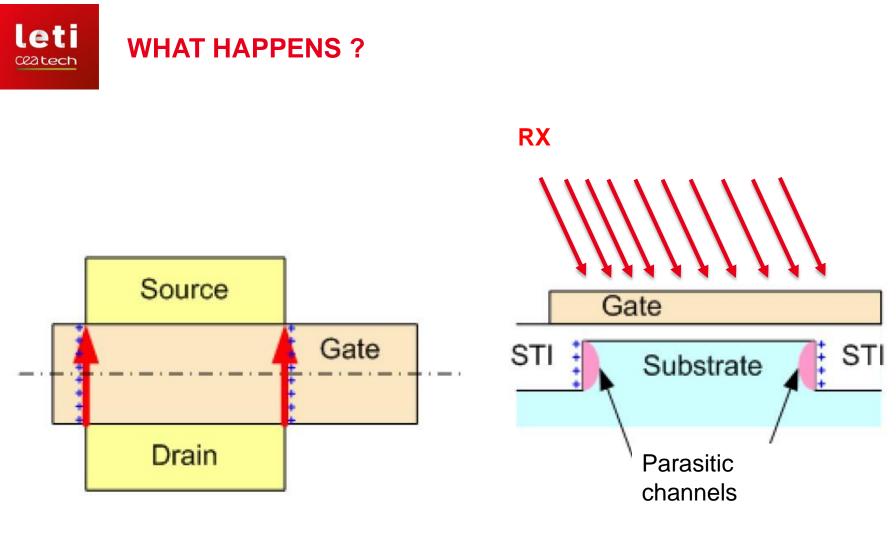

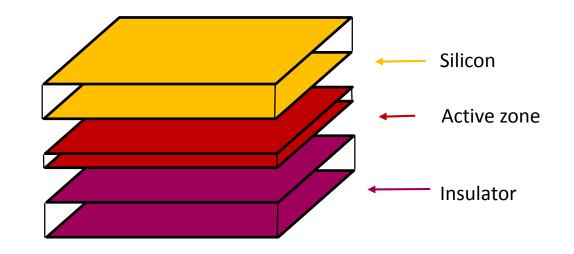

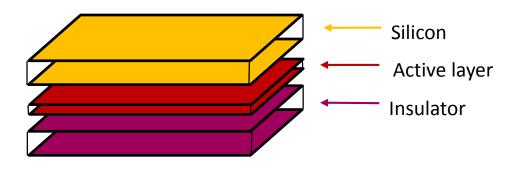

# 6. EXPERIMENTAL COMPARISON AND ANALYSIS OF THE SENSITIVITY TO LASER FAULT INJECTION OF CMOS FD-SOI AND CMOS BULK TECHNOLOGIES

# <u>Jean-Max Dutertre</u> // EMSE

Laser illumination may be used to inject faults into the computations of secure ICs for the purpose of retrieving secret data. The CMOS FD-SOI technology is expected to be less sensitive than the more usual CMOS bulk technology to such laser fault injection attacks. We report in this work an experimental assessment of the interest of using FD-SOI rather than CMOS bulk to decrease laser sensitivity. Our experiments were conducted on test chips at the 28 nm node for both technologies with laser pulse durations in the picosecond and nanosecond ranges.

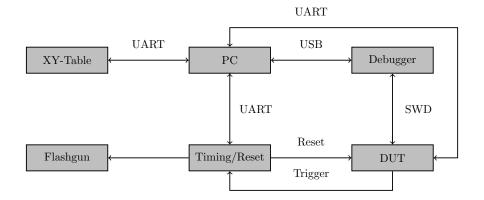

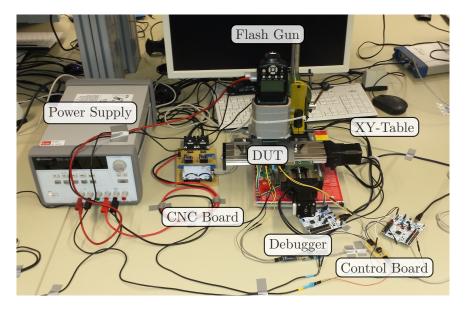

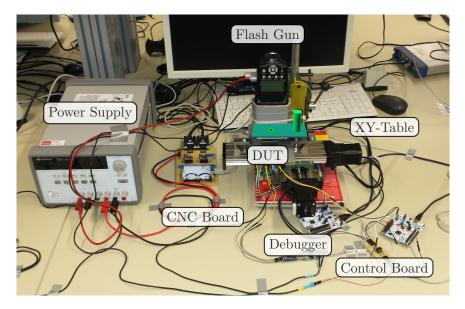

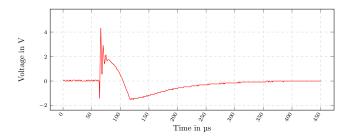

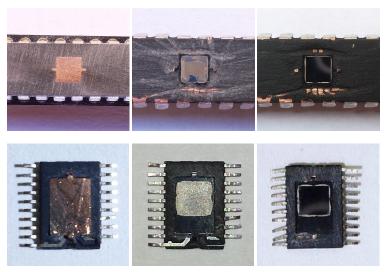

# 7. LOW-COST SETUP FOR LOCALIZED SEMI-INVASIVE OPTICAL FAULT INJECTION ATTACKS

# <u>Michael Gruber</u>, Fabrizio De Santis // Technische Universität München, Oscar M. Guillen // Giesecke & Devrient GmbH Munich

Localized semi-invasive optical fault attacks are nowadays considered to be out of reach for attackers with a limited budget. For this reason, they typically receive lower attention and priority during the security analysis of low-cost devices. Indeed, an optical fault injection setup typically requires expensive equipment which includes at least a laser station, a microscope, and a programmable X-Y table, all of which can quickly add up to several thousand euros. Additionally, a careful handling of toxic chemicals in a protected environment is required to decapsulate the chips under test and gain direct access to the die surface. In this work, we present a low-cost fault injection setup which is capable of producing localized faults in modern 8-bit and 32-bit microcontrollers, does not require handling hazardous substances or wearing protective eyeware, and would set back an attacker only a couple hundred euros. Finally, we show that the type of faults which are obtained from such a low-cost setup can be exploited to successfully attack real-world cryptographic implementations, such that of the NSA's Speck lightweight block cipher.

## 8. FAULTS ATTACKS ON SOCS

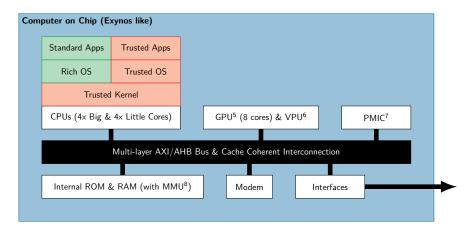

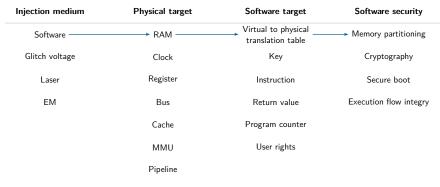

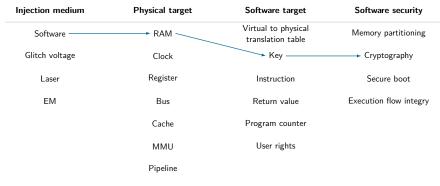

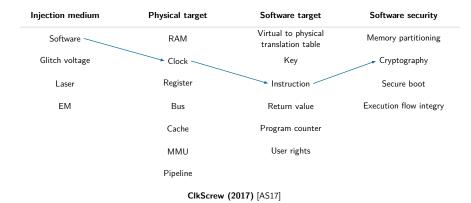

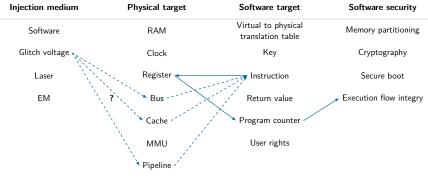

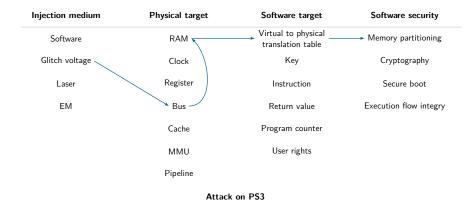

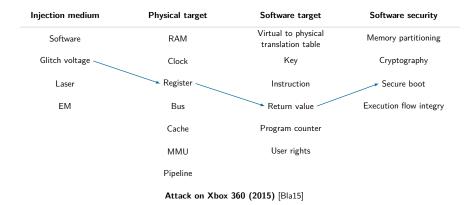

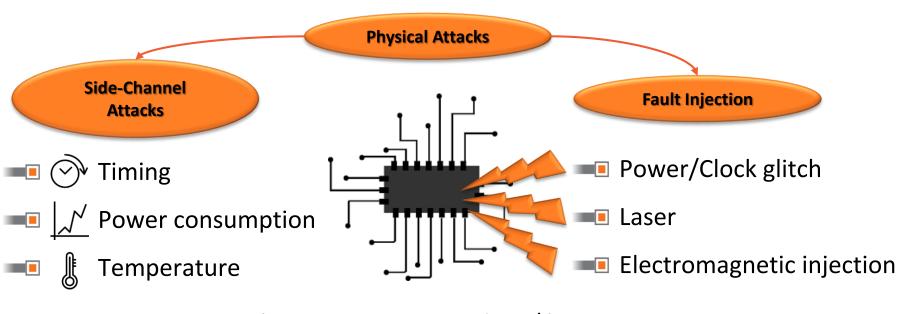

# Thomas Trouchkine, Guillaume Bouffard // ANSSI, Jessy Clédière // CEA Tech

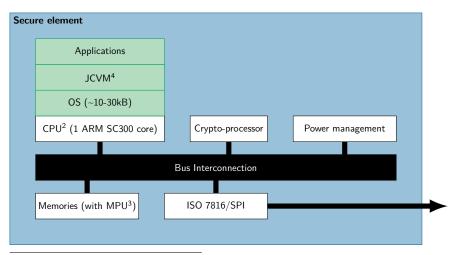

Systems on Chip (SoC) are complex integrated circuits which contain a many components (processors, controllers...). They are present in a lot of common systems like smartphones or IoT devices. These systems manipulate sensitive data (bank, health or ID). To ensure the condentiality of these data, several security mechanisms (mostly software) are implemented in them such as Secure Boot, Trusted Environment Execution or Memory Partioning.

Despite the fact SoCs are assumed to be secured from a software point of view they don't integrate any mitigation against hardware attacks (side-channels and faults). For this presentation, we'll focus on fault injection attacks. Due to this lack of security, several faults based attacks on SoCs are emerging. These attacks explore new attack paths mixing fault injection and software exploitation to undermine security mechanisms.

To execute sensitive operations, the chip designers are looking to certify their SoCs. In order to understand the underlying challenges, this presentation will focus on the issues of the hardware security on SoCs. We will present a modelization of this new attack paths and some remarkable attacks which put forward the complexity of mixing a hardware fault injection with a software exploitation. Our final goal is to be able to evaluate the resistance of SoCs against this new threats.

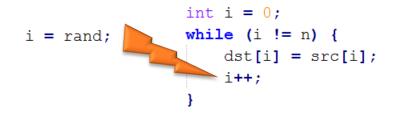

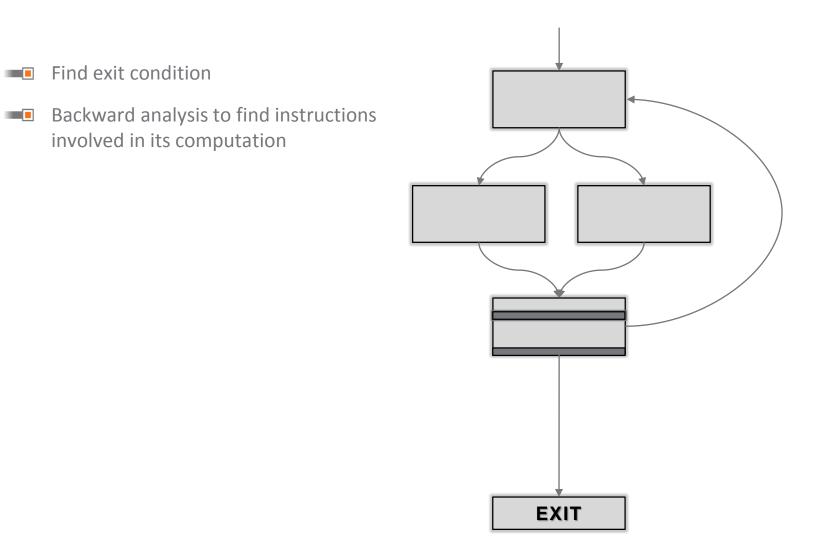

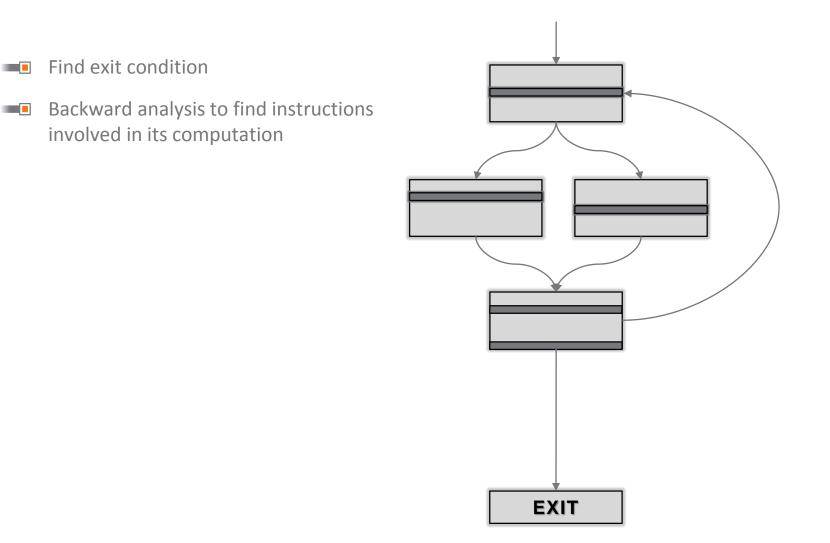

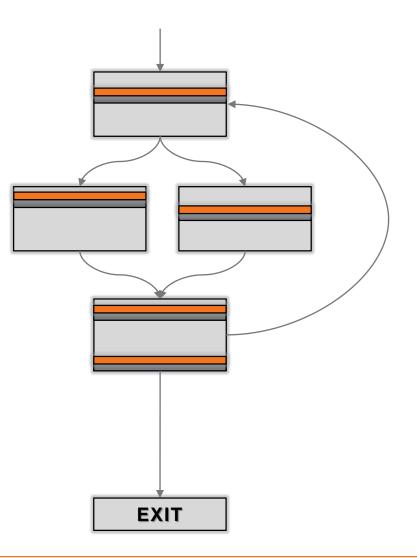

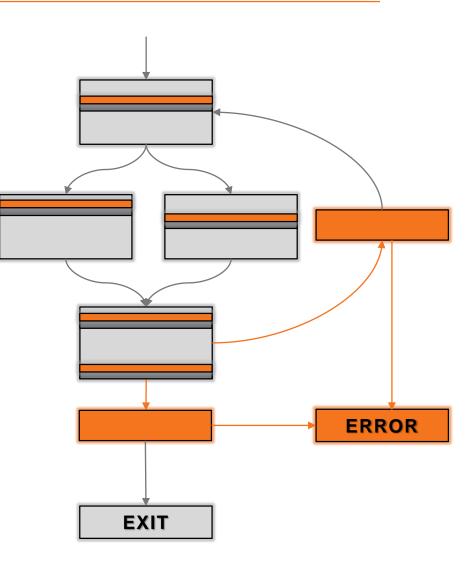

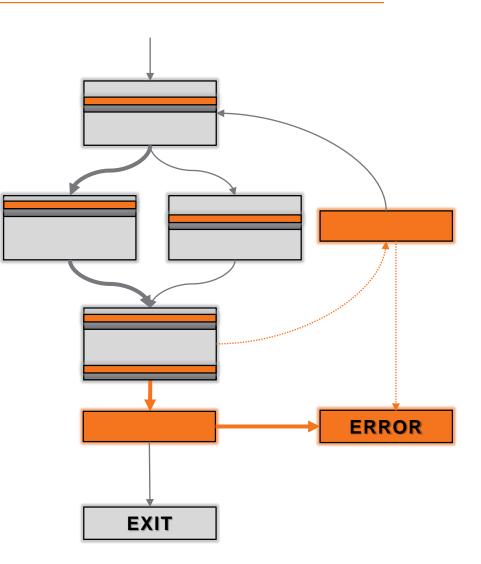

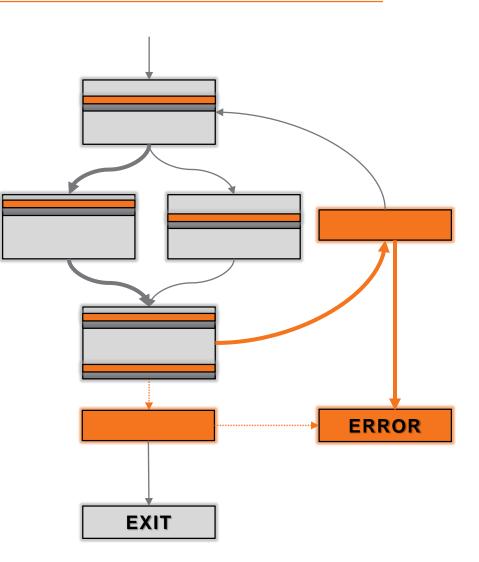

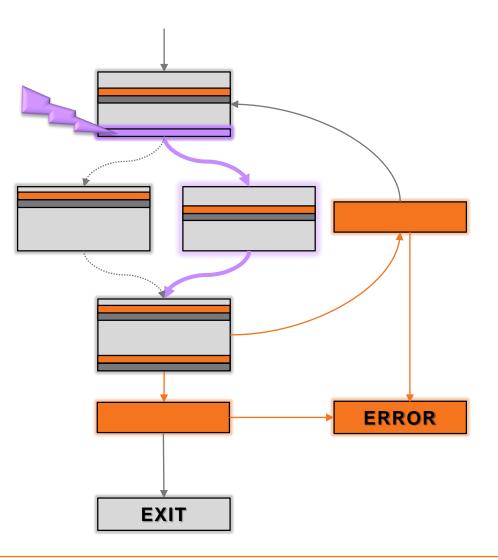

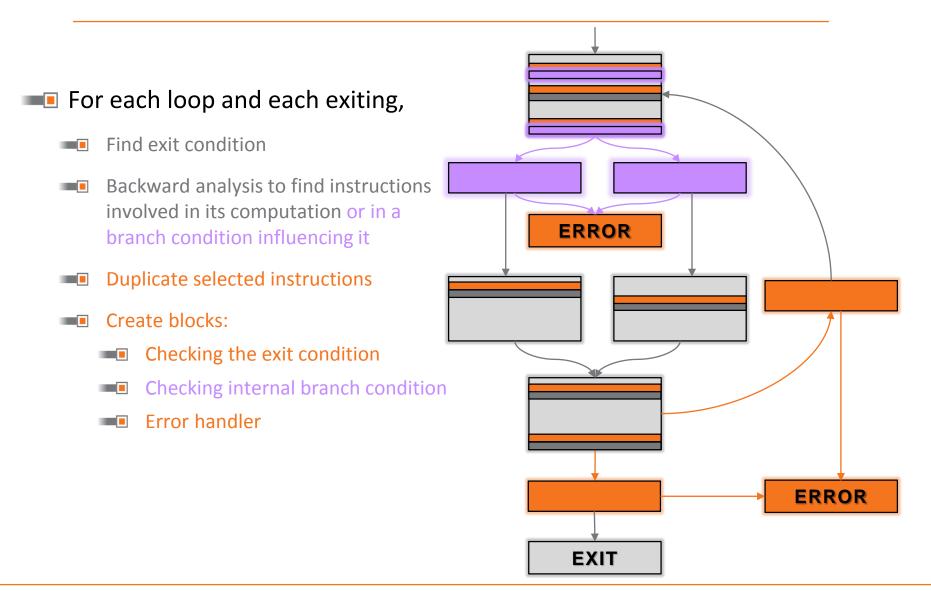

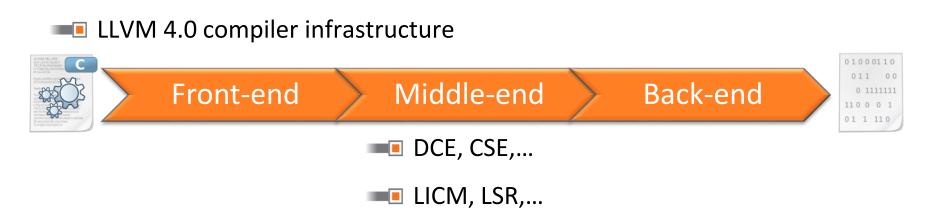

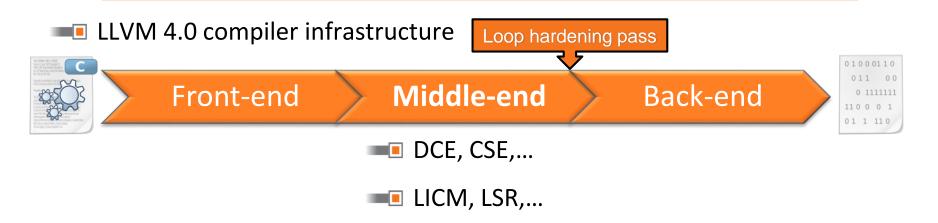

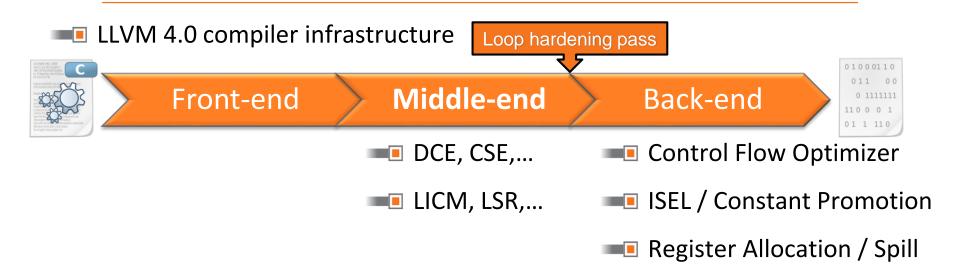

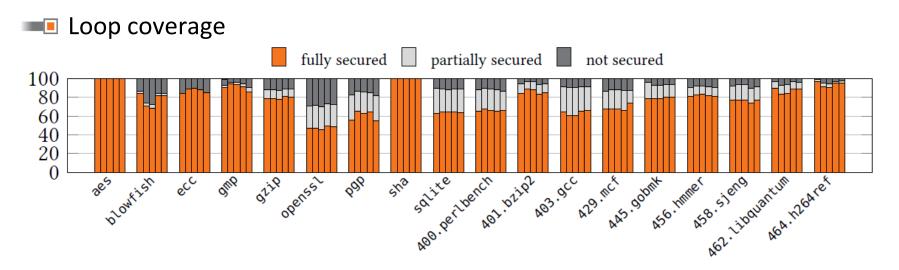

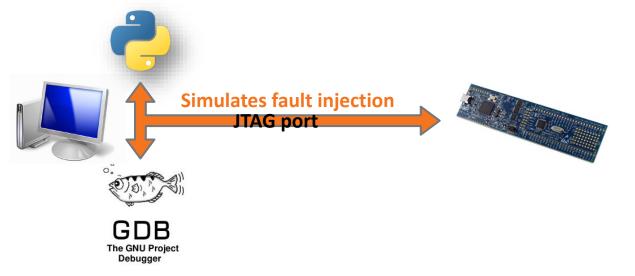

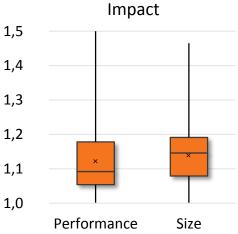

## 9. COMPILER-ASSISTED LOOP HARDENING AGAINST FAULT ATTACKS

## Julien Proy // INVIA

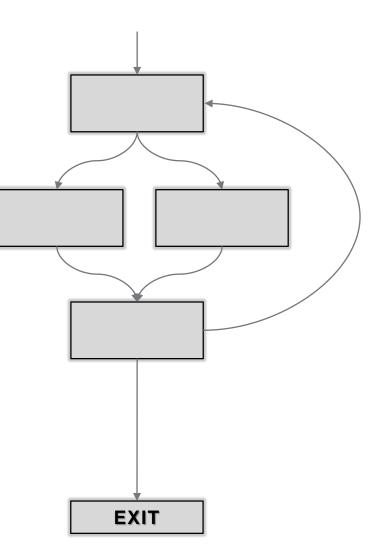

Secure elements widely used in smartphones, digital consumer electronics, payment systems are subject to fault attacks. To thwart such attacks, software protections are manually inserted requiring experts and time. The explosion of the Internet of Things (IoT) in home, business and public spaces motivates the hardening of a wider class of applications, and the need to offer security solutions to non-experts. This paper addresses the automated protection of loops at compilation time, covering

the widest range of control- and data-flow patterns, in both shape and complexity. The security property we consider is that a sensitive loop must always perform the expected number of iterations, otherwise an attack must be reported. We propose a generic compile-time loop hardening scheme based on the duplication of termination conditions and of the computations involved in the evaluation of such conditions. We also investigate how to preserve the security property along the compilation flow while enabling aggressive optimizations. We implemented this algorithm in LLVM 4.0, at the Intermediate Representation (IR) level in the backend. On average, the compiler automatically hardens 95% of the sensitive loops of typical security benchmarks, and 98% of these loops are shown to be robust to simulated faults. Performance and code size overhead remain quite affordable, at 12.5% and 14% respectively.

# // SESSION // SIDE-CHANNEL ANALYSIS: ATTACKS & PROTECTIONS (II)

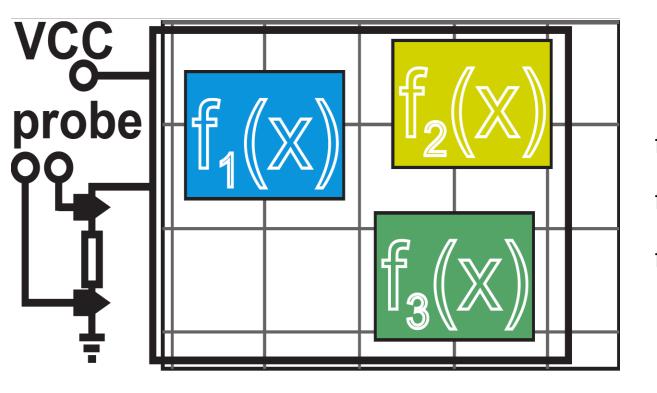

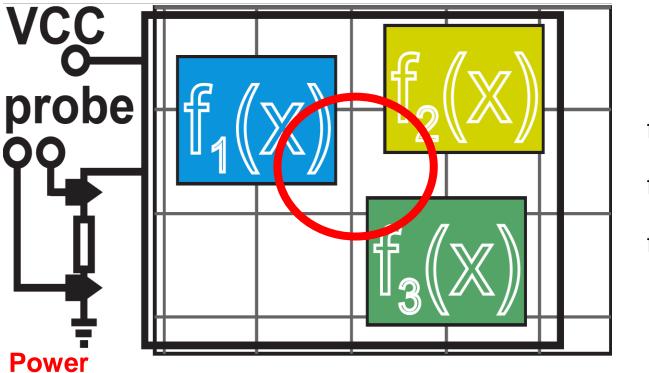

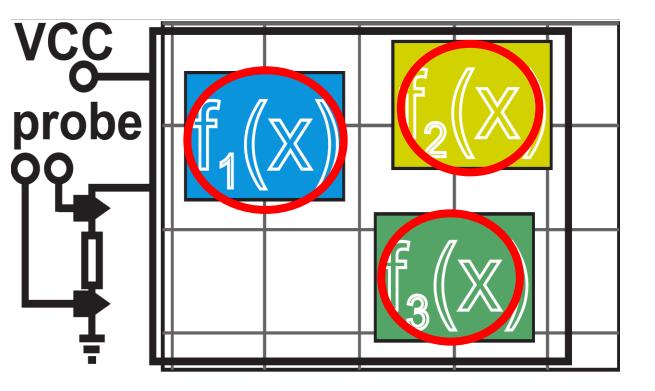

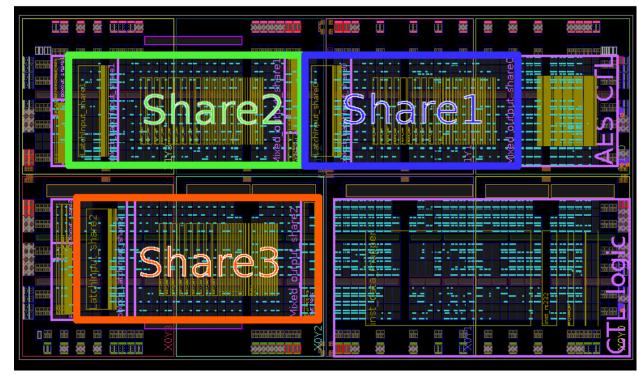

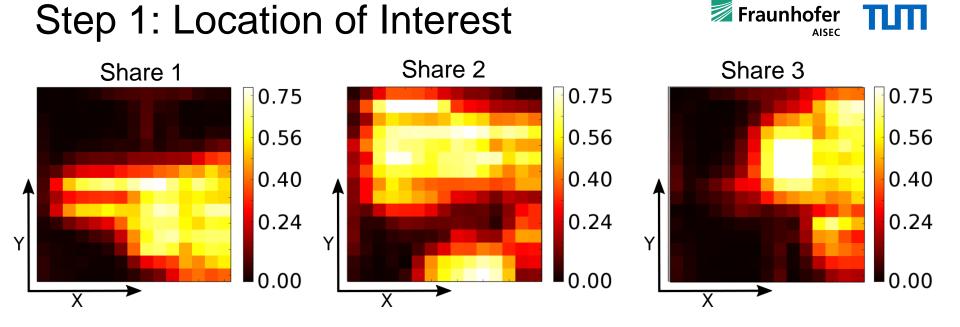

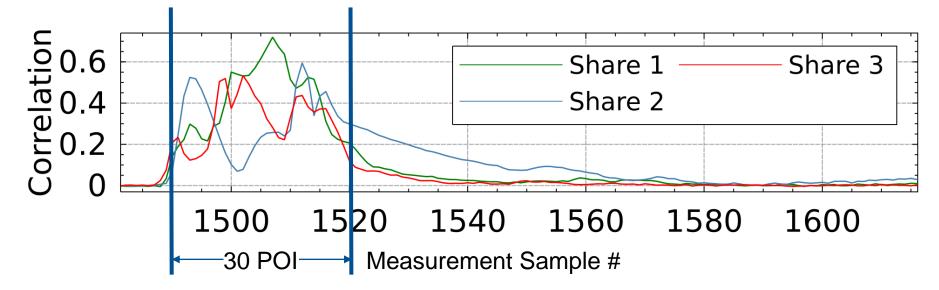

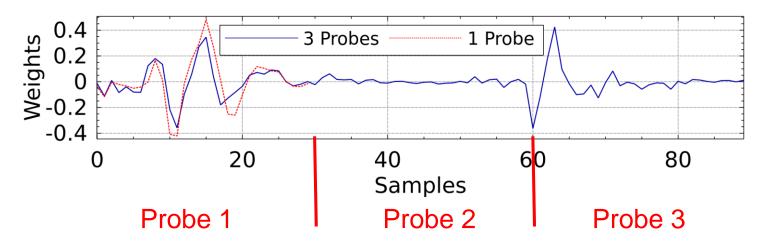

# **10.** DIVIDING THE THRESHOLD: MULTI-PROBE LOCALIZED EM ANALYSIS ON THRESHOLD IMPLEMENTATIONS

# Georg SIGL // Technische Universität München

Cryptographic implementations typically need to be secured to retain their secrets in the presence of attacks. As a countermeasure to prevent side-channel attacks, threshold implementations are a commonly encountered concept. They resemble a multi-party computation, where the value is split in independent shares and processed separately.

In this work, we challenge the underlying security assumption that observing these individually processed values is difficult. We observe leakage by spatially separating the shares on an FPGA using multiple electro-magnetic (EM) probes simultaneously for localized EM analysis. We experimentally verify that the security gain is 238 times less with this method when compared to the power side-channel. In total, we only need 4,300 traces to break a second-order secure implementation.

Moreover, such a reduction in protection level is only possible when using multiple probes and applying our attack strategy which is based on state-of-the-art template attacks. This attack can easily be carried out by any attacker at the expense of buying more probes which emphasizes the danger of such attacks.

# **11. SIDE-CHANNEL ROBUSTNESS ANALYSIS OF MASKED PROGRAMS**

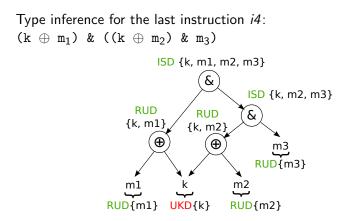

# <u>Inès Ben EL Ouahma</u>, Quentin Meunier, Karine Heydemann, Emmanuelle Encrenaz // Sorbonne Universités, LIP6.

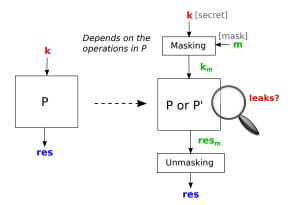

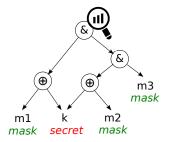

Masking is a popular countermeasure against side-channel attacks, which randomizes secret data with random and uniform variables called masks. At software level, masking is usually added in the source code and its effectiveness needs to be verified. Such an analysis must be performed at the assembly level because the compilation flow may alter the added protections.

In this talk, we present a method to check side-channel robustness of masked programs using a symbolic approach. The aim is to verify that the result of each intermediate computation is statistically independent from secret variables. We propose to infer the distribution type of the result

by analyzing the expression of the computation using a set of inference rules. Our inference system is sound, yet not complete, and is enriched with a bit level analysis that allows to state statistical independency in more cases. Currently our method can analyze compiled and annotated codes which are masked at first order. The talk will give experimental results comparing analyzed programs at source and assembly level, as well as on a masked AES.

# // SESSION // ADVANCES IN SECURE SYSTEMS

# 1. LIGHTWEIGHT AND SECURE SCHEME TO MITIGATE DENIAL-OF-SERVICE ON WAKE-UP RADIOS FOR IOT DEVICES

# Maxime Montoya, Simone Bacles-Min, Anca Molnos, Jacques Fournier // CEA Tech

Wake-up radios are mechanisms that control the sleep and active modes of energy-constrained Internet of Things (IoT) nodes which have to be operational during a long time. These radios detect pre-determined wake-up tokens and switch the devices to an active state. Such systems are vulnerable to a kind of Denial-of-Service attacks called Denial-of-Sleep, where attackers continuously send wake-up tokens to deplete the battery of the nodes. We propose a protocol to mitigate these attacks that includes a novel solution to generate hard-to-guess wake-up tokens at every wake-up. This protocol can be used together with many common communication protocols for the IoT such as LoRa, Sigfox, or ZigBee. Simulations show that under standard operating conditions, it has a negligible energy overhead (0.03%), while it increases the lifetime of an IoT node by more than 40 times under Denial-of-Sleep attack. Finally, we compare our protocol to related work against Denial-of-Sleep attacks, and explain why it is both more resilient and more energy-efficient than existing approaches.

# 2. ML-ENHANCED FIA DETECTION

# Robert NGuyen, Nicolas Bruneau, Xuan Thuy Ngo, Michel Le Rolland, Adrien Facon // Secure-IC

Today, chips are equipped with multiple sensors, of different kinds, some with primary goal data acquisition functionality, but also sensors for adaptation to the environment (like battery level, temperature, wireless activity in the neighborhood, etc.). All those can advantageously complement security sensors. Security sensors watch events which would hint for attack conditions. It can consist in:

- Abnormal physical operating conditions in terms of temperature, voltage, clock frequency, reset line stability, etc.

- Abnormal activity (detection of port scanning, unexpected data flowing out the device, load of processor, strange failure signals such as multiple segmentation violations within short period of time, etc.)

All these pieces of information can be processed to decide whether the device shall be considered in a nominal or in an unsafe environment. This is where AI comes into play. Indeed, AI is the solution to analyze fuzzy information arising from "big data" measurements collections. Merging heterogeneous signals allows to leverage unexploited sources of information such as randomness quality, tiny clock modulation, noise statistic moments modification for security event detection. Moreover for security chips, this AI shall run within the chips for integrity and data reduction efficiency. In this case, even data rate and data volume are high, quick decisions must be taken. Indeed, a laser or a malware attack requires few clock cycles to exploit the chip: installing a backdoor is a matter of kilobytes of payload.

Secure-IC's Smart Monitor is an AI-enabled on-chip security supervisor improving both security event detection, diagnostic and decision-making process. This on-chip security headquarter creates collective intelligence and coherence between IPs (analogic or digital) and other whistleblowers and weak signals (software or hardware) improving both security event detection, analysis, diagnostic and decision-making process. It allows to gain advantage over attackers and interestingly to perform rich Business Intelligence.

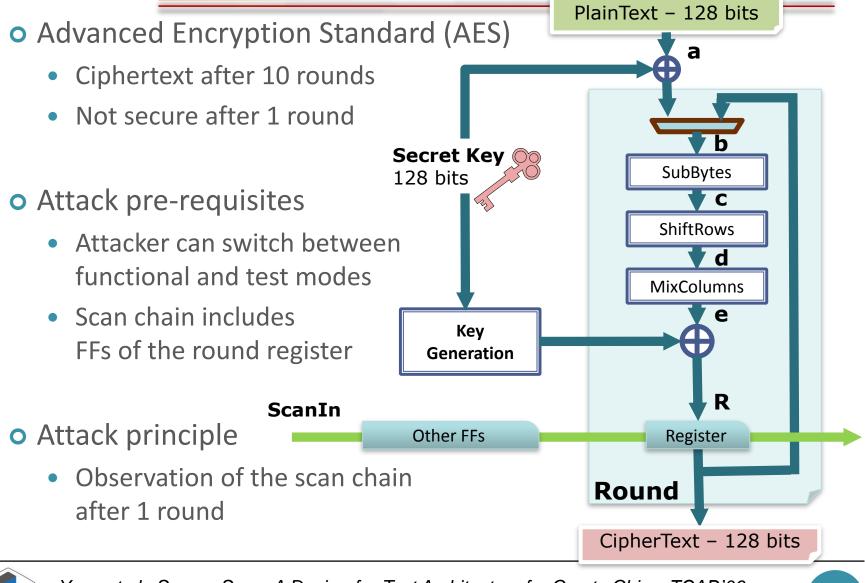

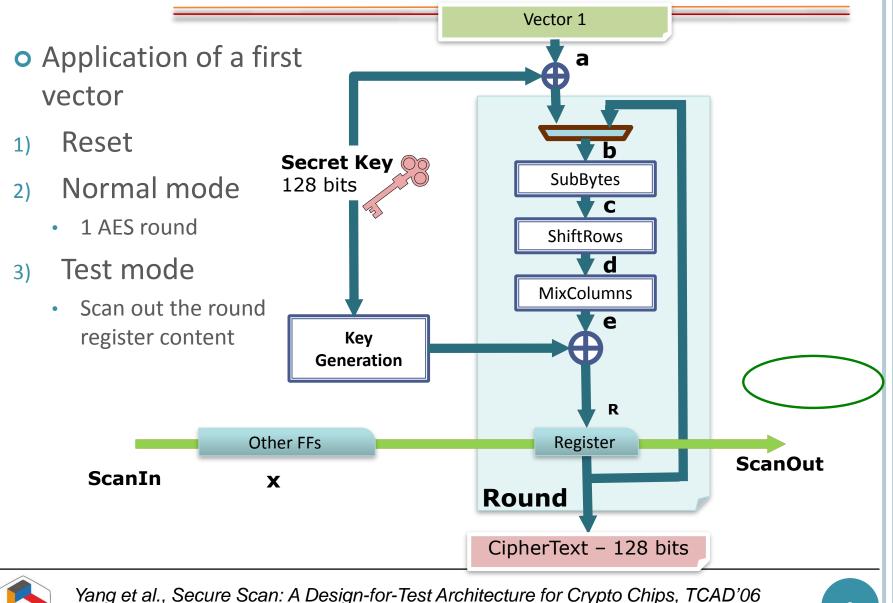

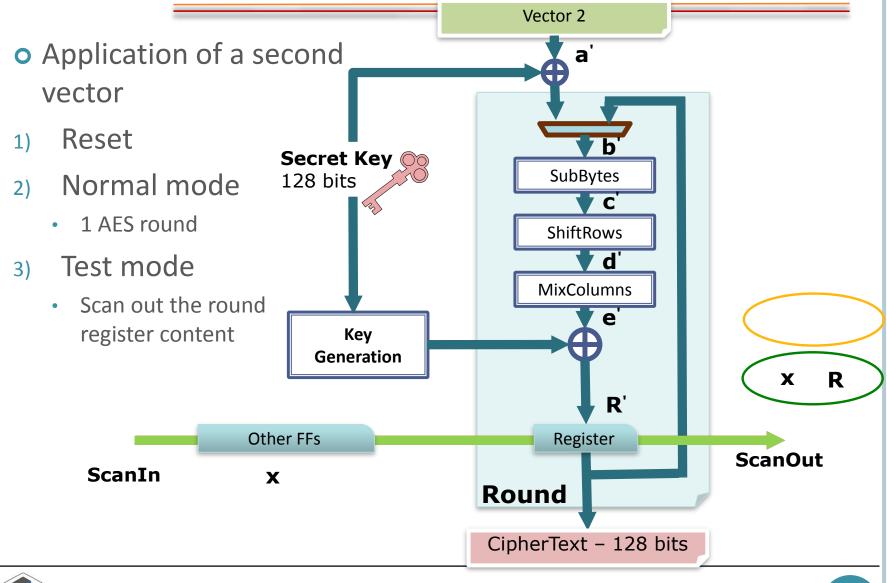

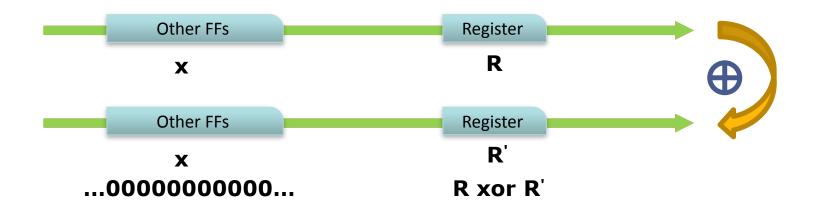

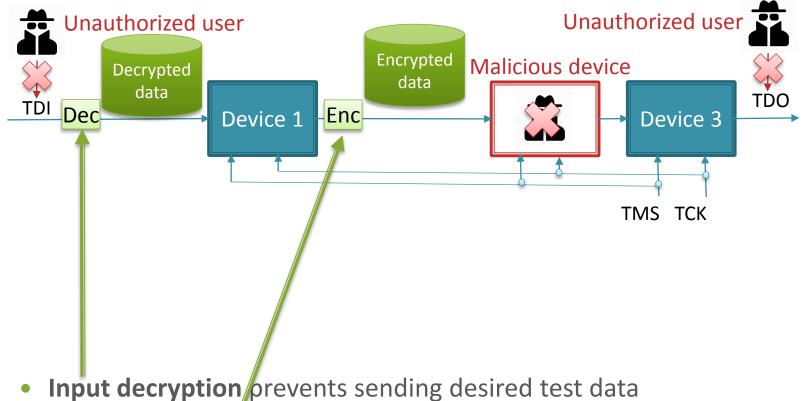

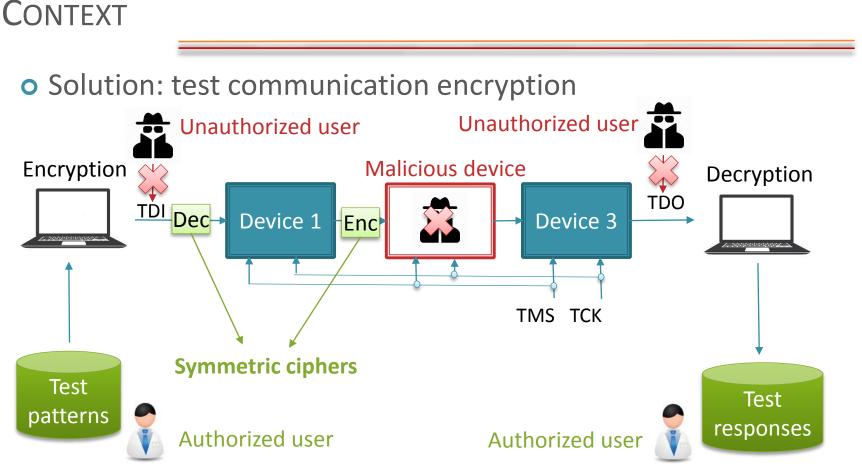

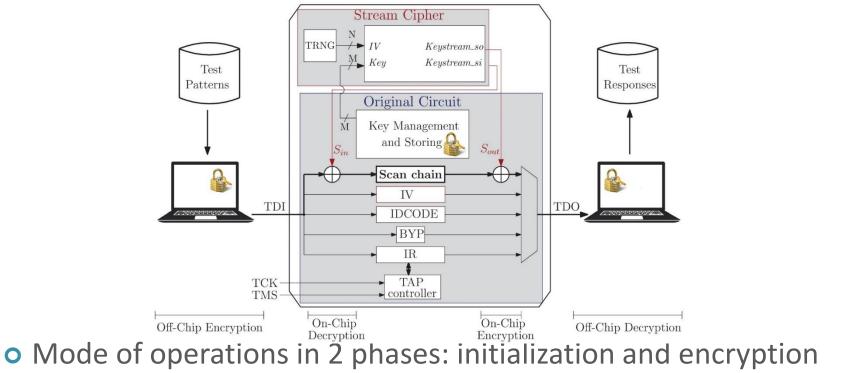

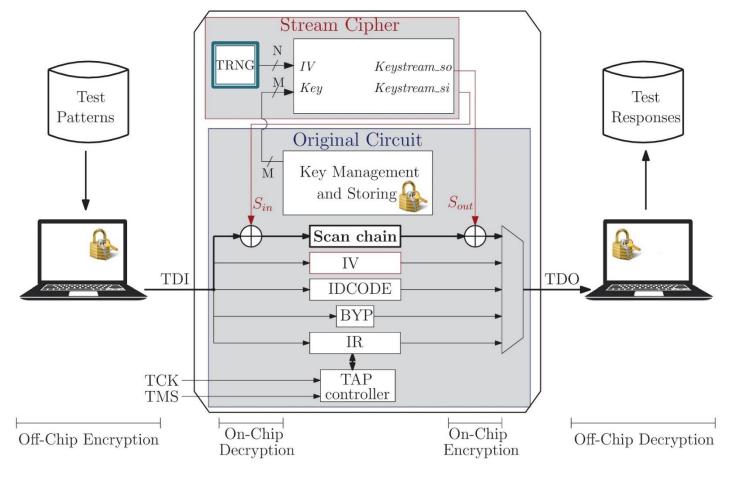

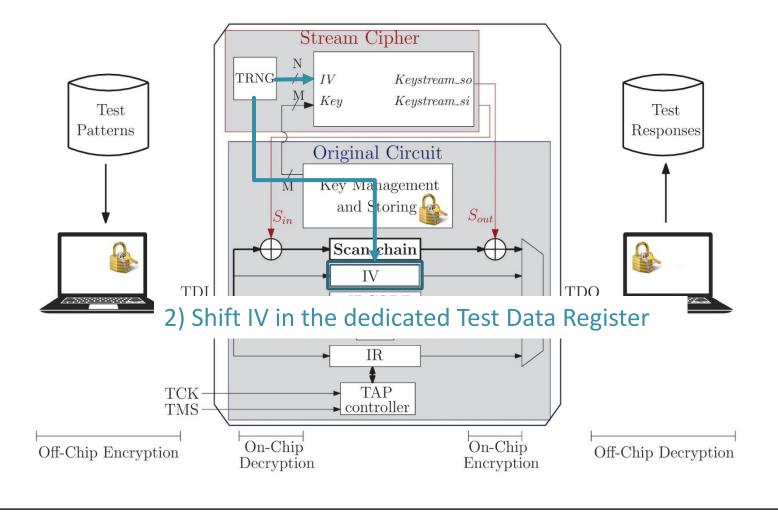

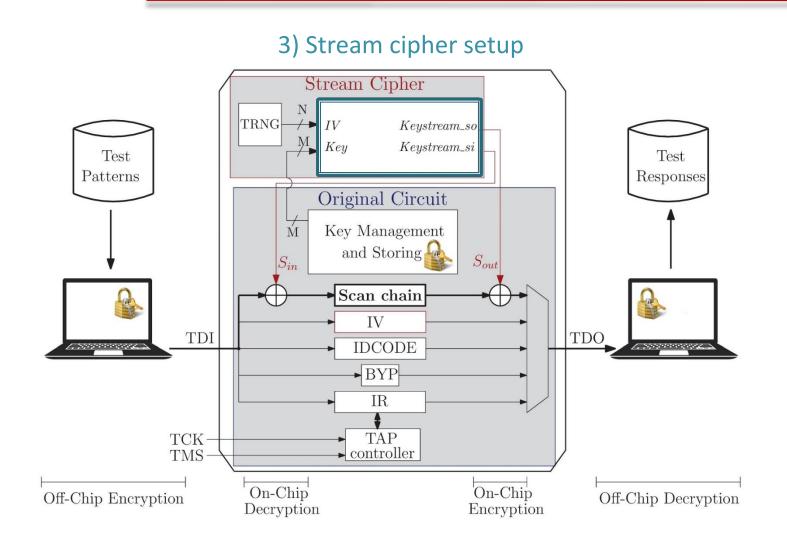

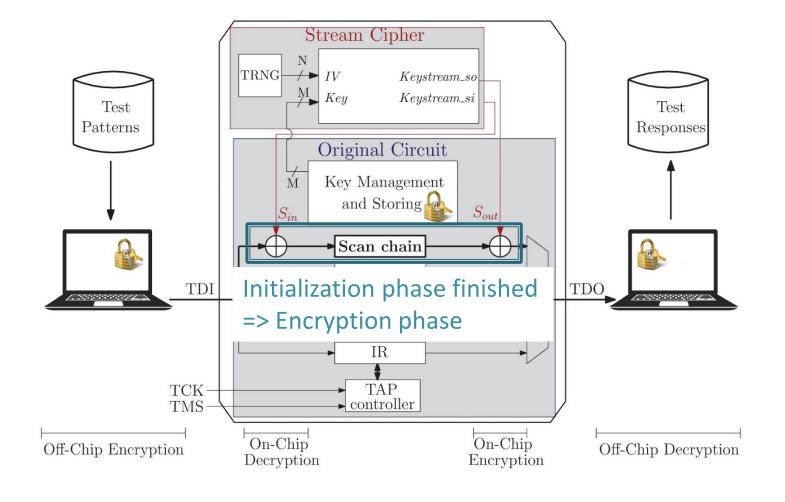

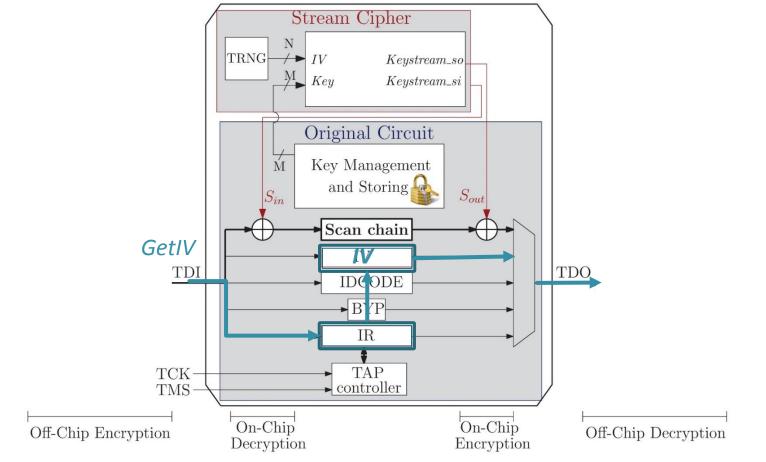

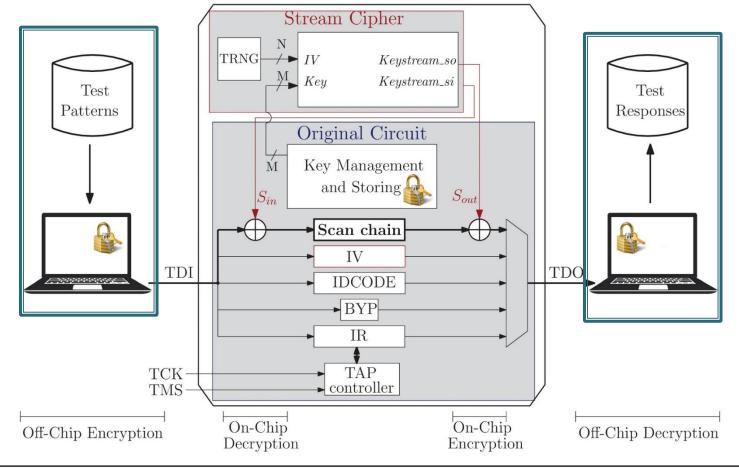

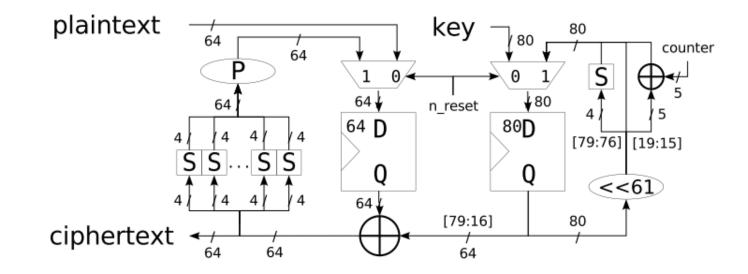

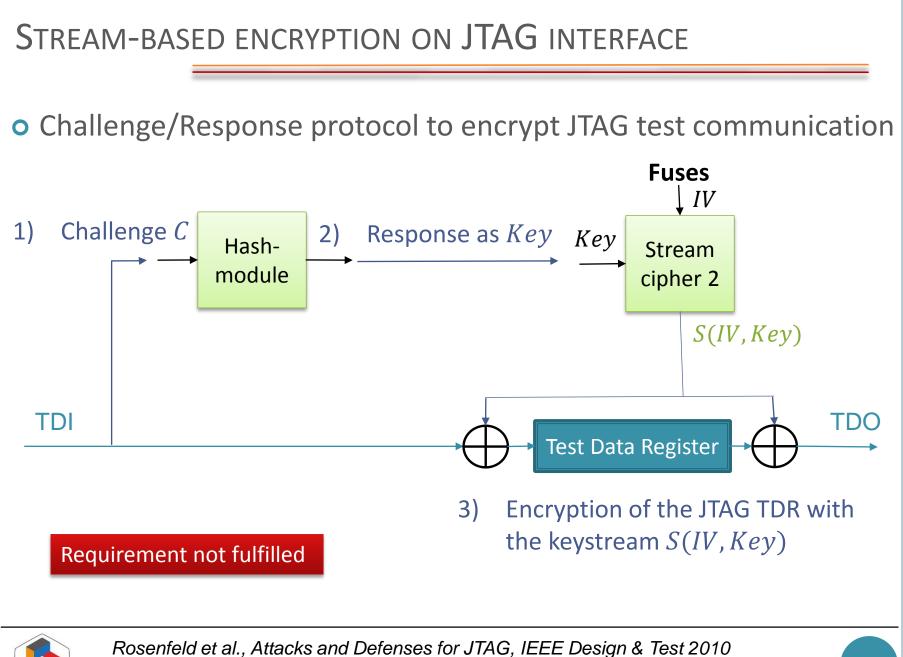

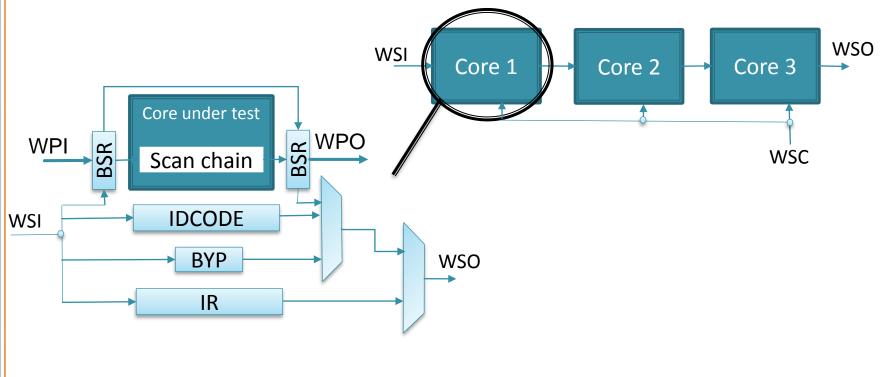

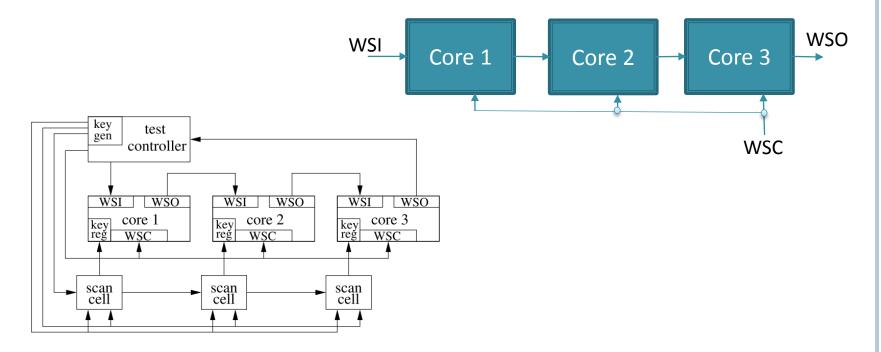

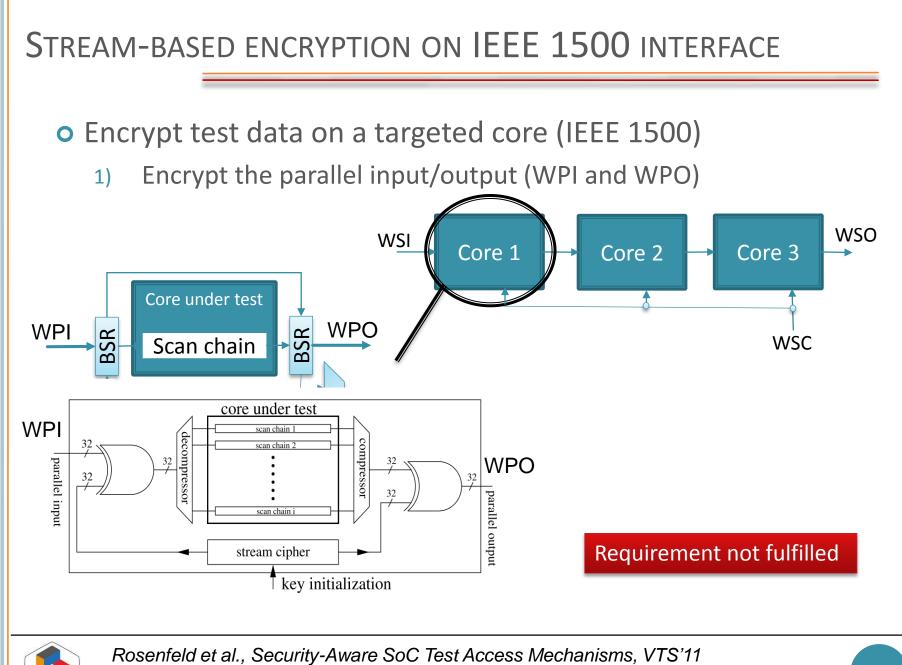

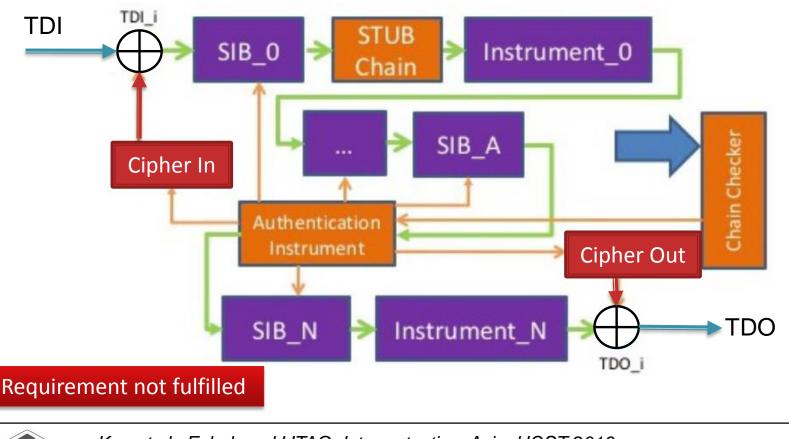

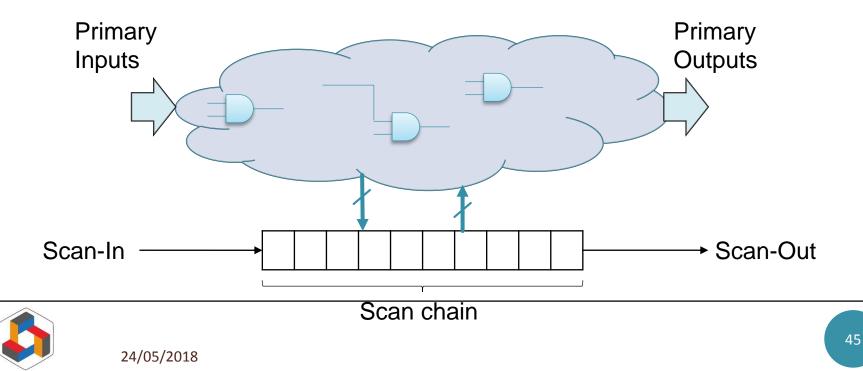

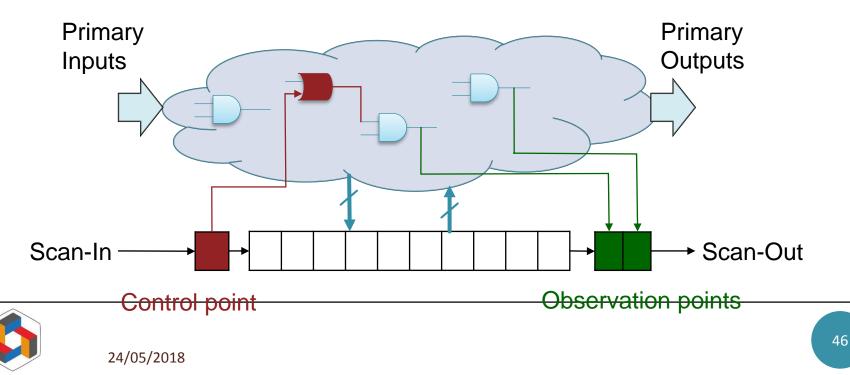

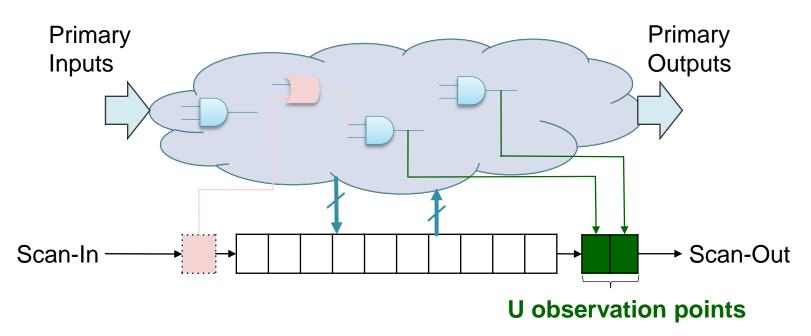

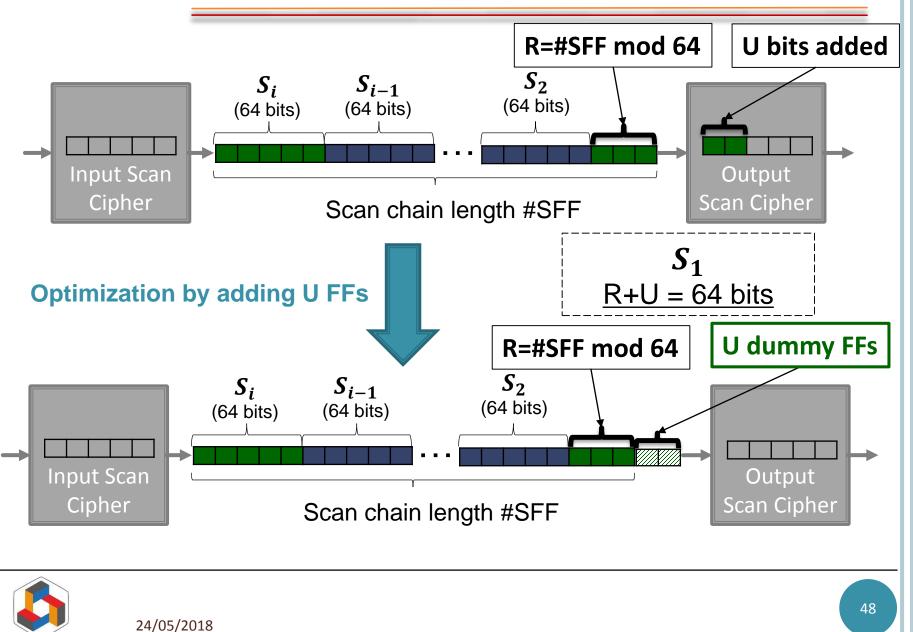

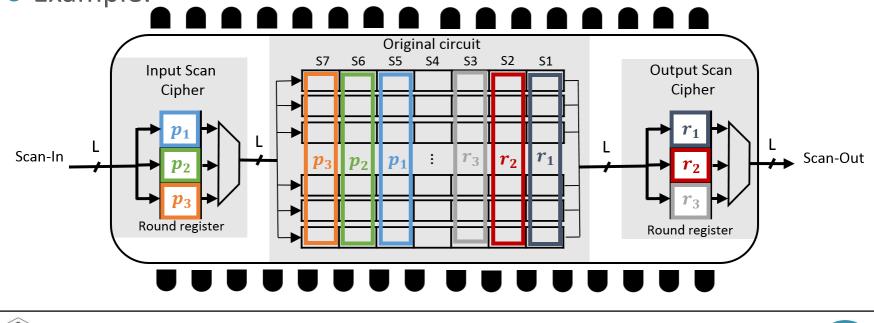

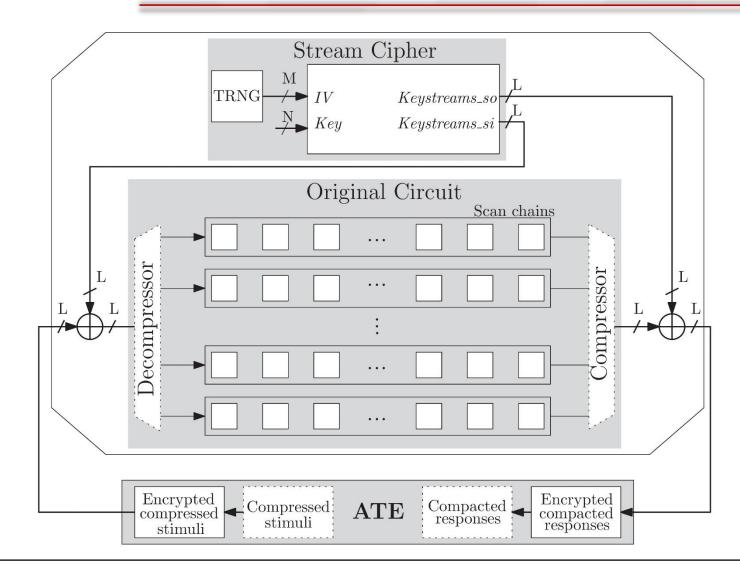

## 3. SCAN CHAIN ENCRYPTION, A COUNTERMEASURE AGAINST SCAN ATTACKS

# Mathieu Da Silva // LIRMM

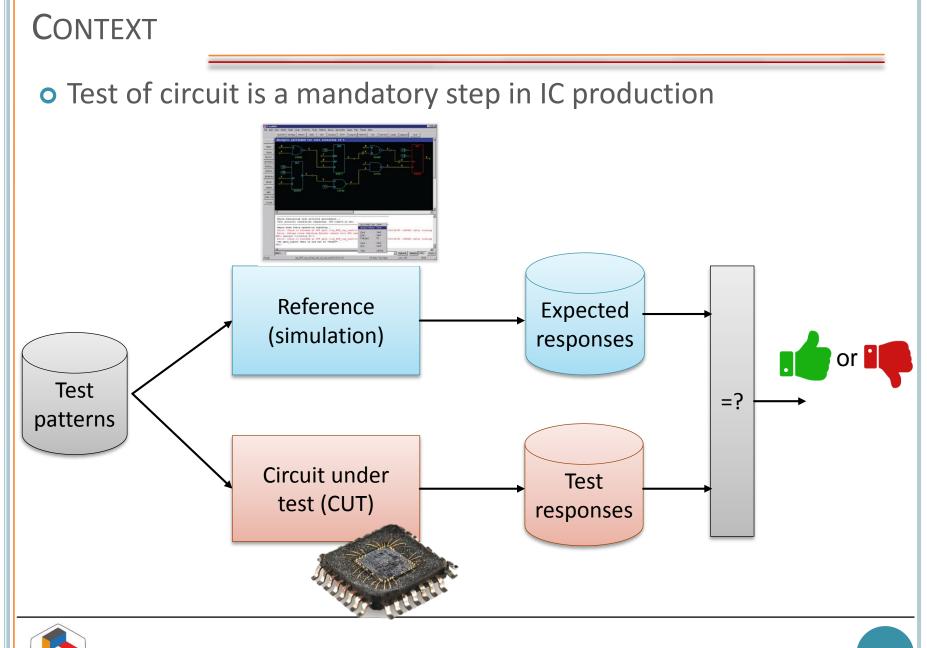

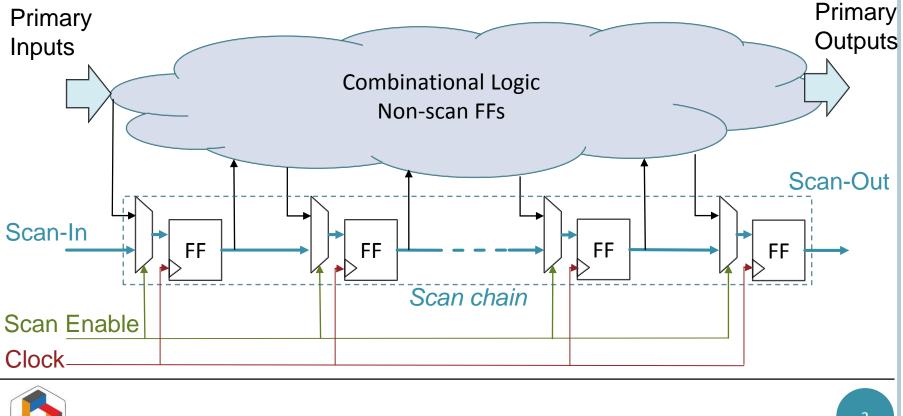

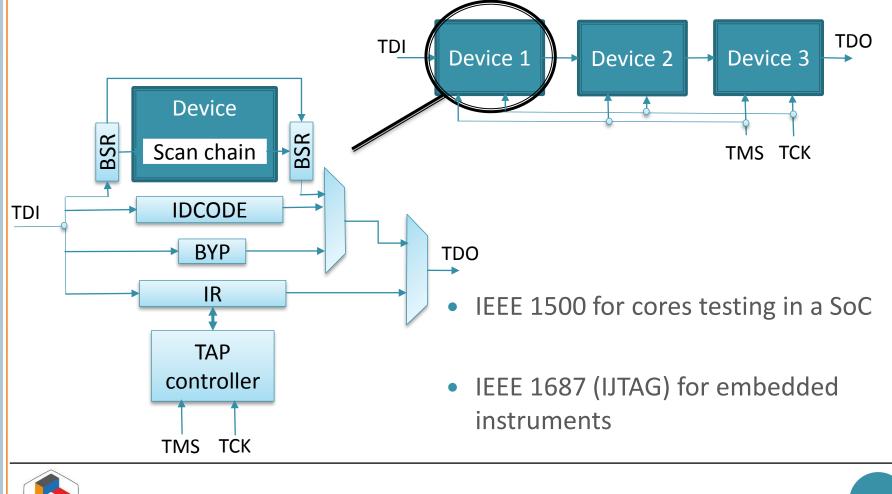

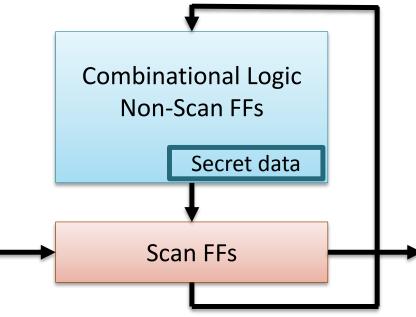

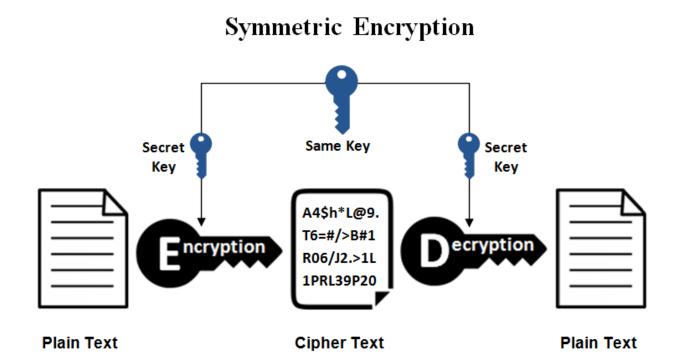

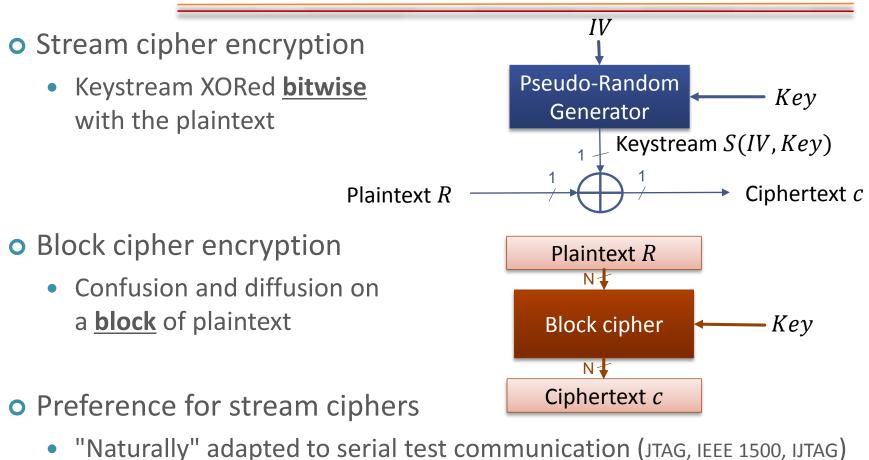

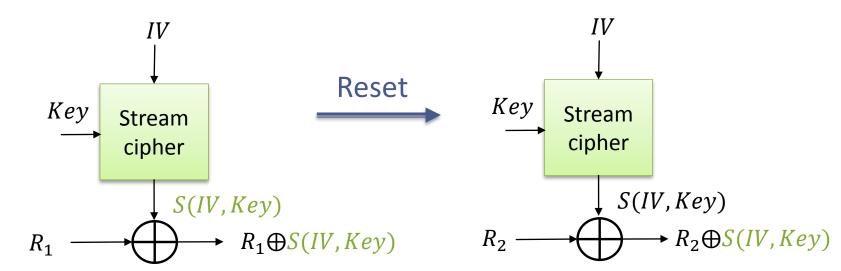

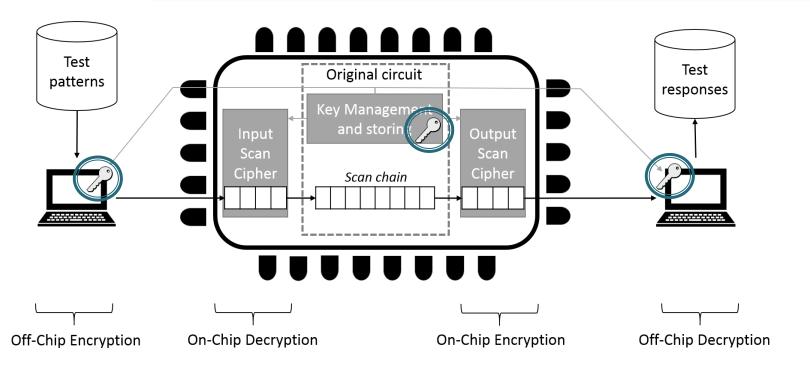

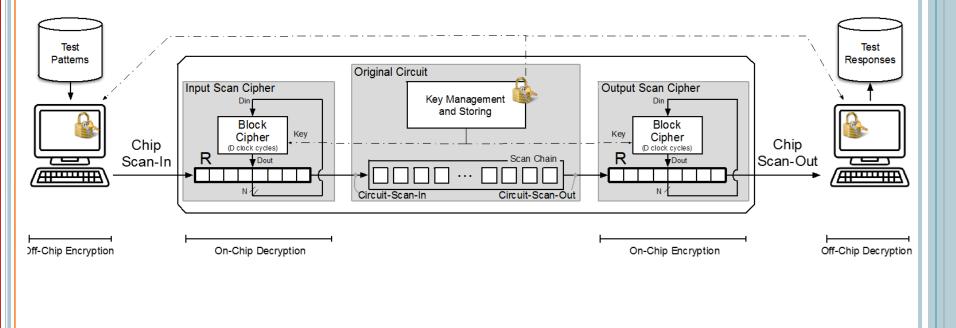

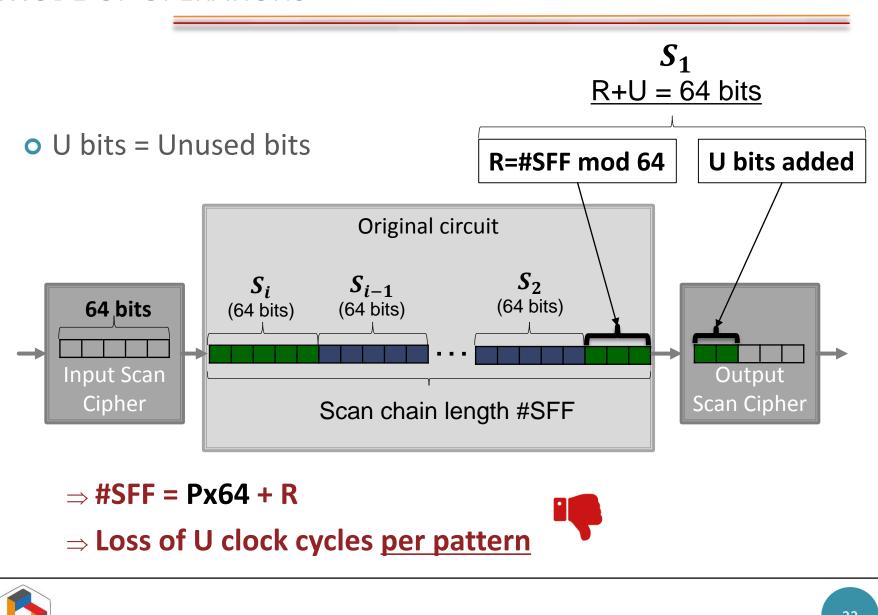

Security in Integrated Circuits (ICs) domain is an important challenge, especially with regard to the side channel offered by test infrastructures. Test interfaces allow accessing the internal states of the IC by mean of the scan chains for testing and debugging purposes. In terms of security, scan chains are however a potential source of leakage that can be exploited by attackers. For instance, they can steal secret information, analyze the internal states of the circuit in order to help reverse-engineering, or modify the circuit operations. A countermeasure against such attacks is to on-chip encrypt the data flowing through the scan chains. Two types of ciphers can be used: either stream ciphers or block ciphers. Both have pros and cons in terms of performance and security.

# // SESSION // SECURITY ASSESSMENT, CHARACTERIZATION & TEST

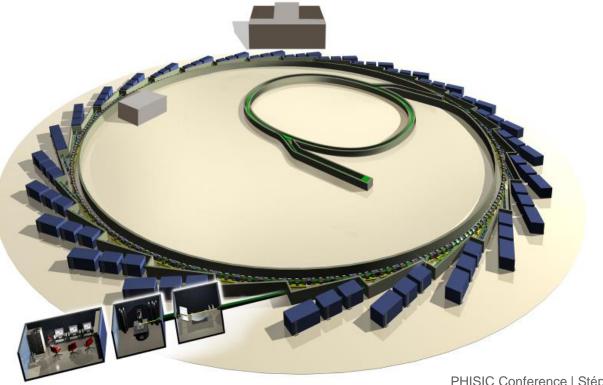

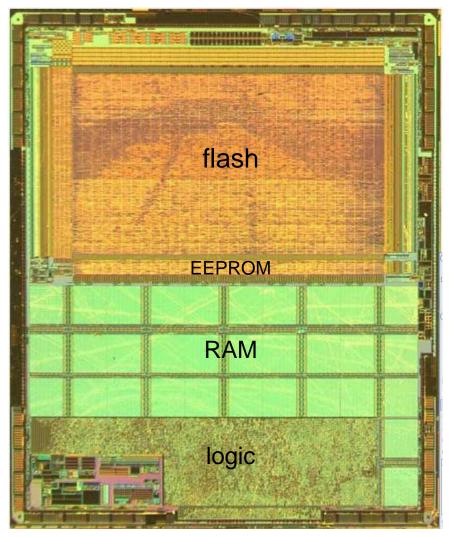

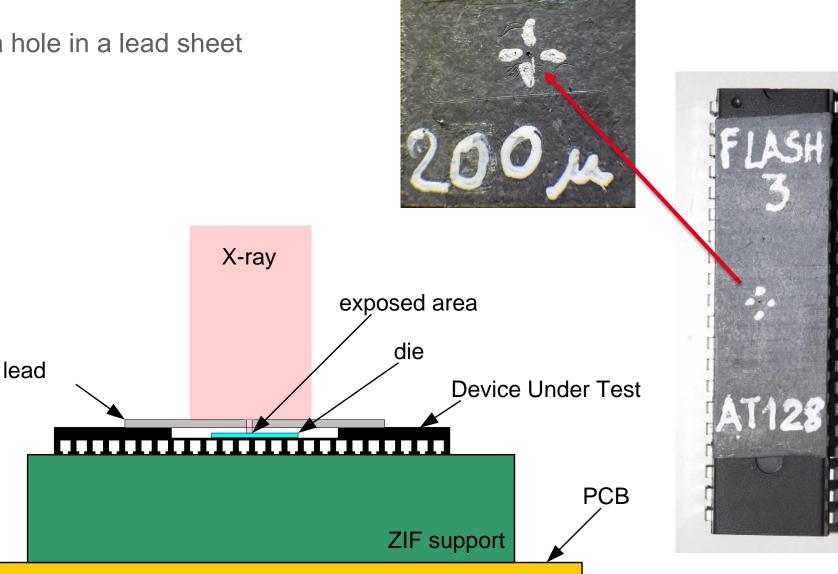

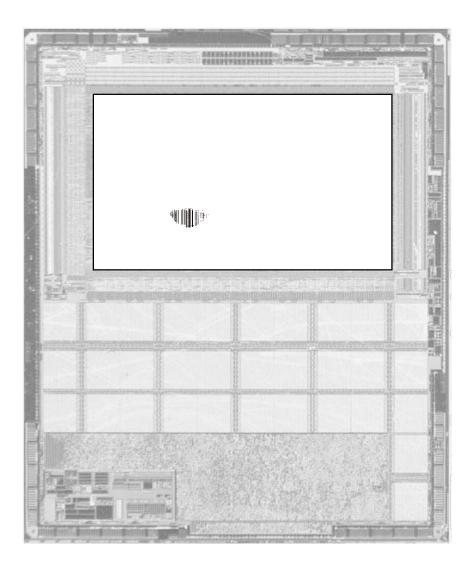

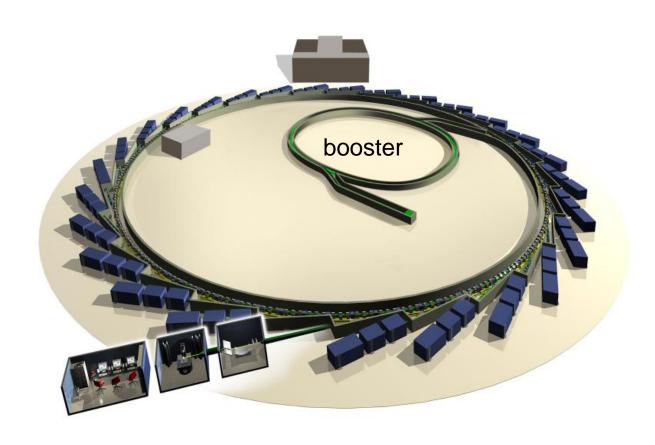

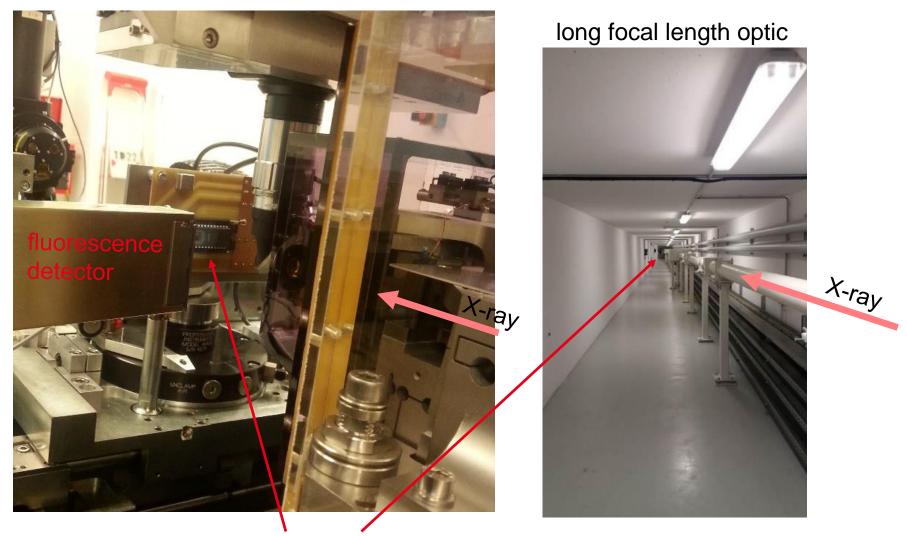

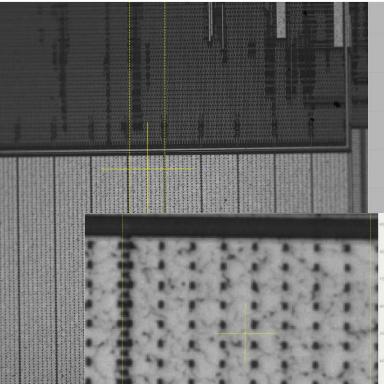

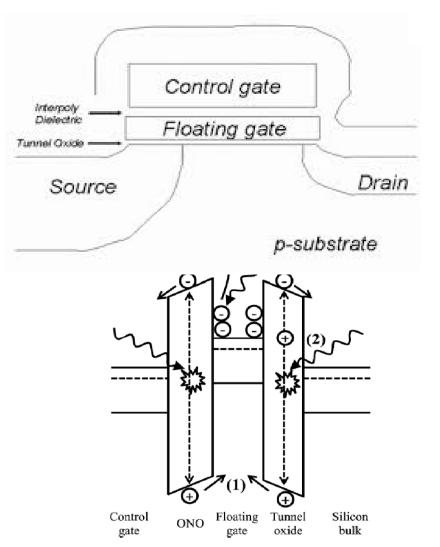

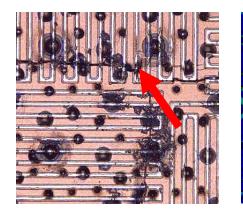

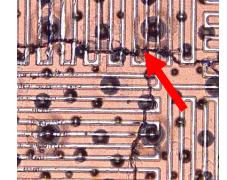

# 4. INTEGRATED CIRCUIT MODIFICATION WITH FOCALIZED X-RAYS BEAM

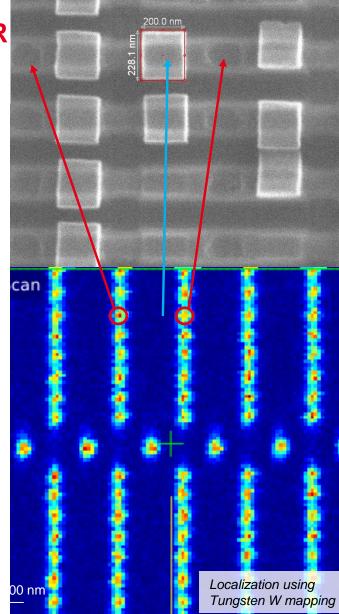

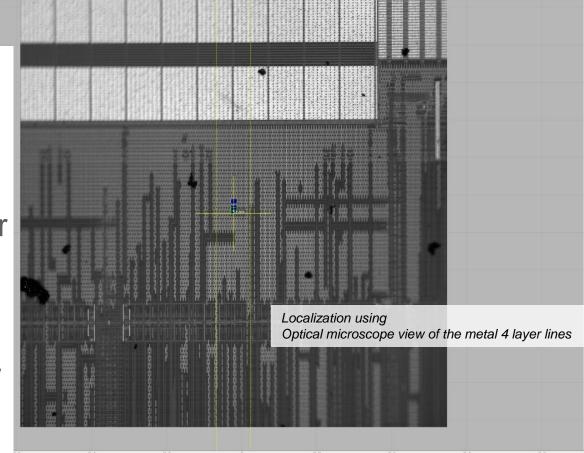

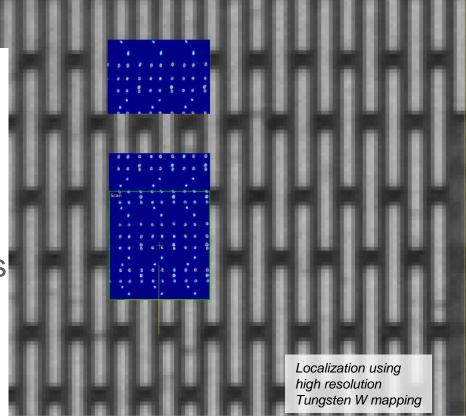

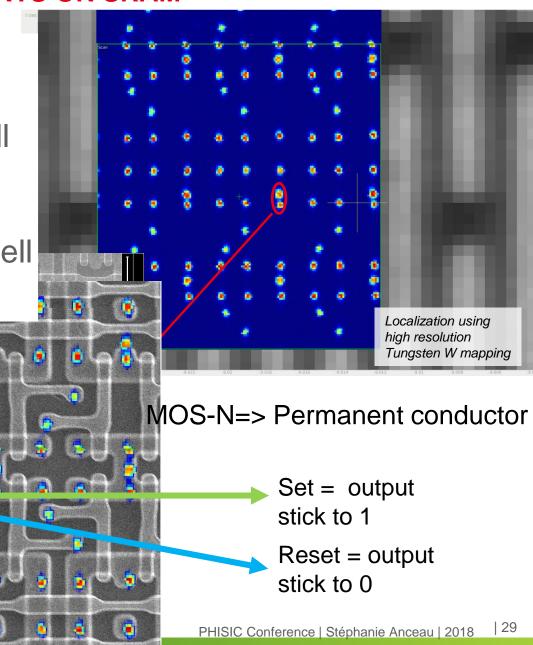

# Stéphanie Anceau // CEA Tech

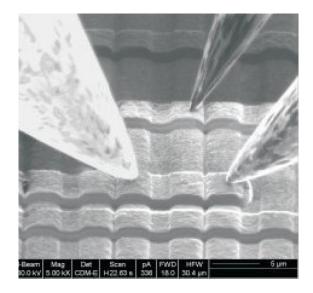

The understanding and conception of electronic devices require tools to modify these devices after their fabrication. A device failure or a functional bug require to modify the component behavior in order to find the corresponding problem. This modification of the integrated circuit is classically done with a Focused Ion Beam (FIB). This equipment permits to etch materials and deposit conductive or insulator materials, which allows to modify the interconnections of the integrated circuit. This operation is called circuit edit because the device can be reconfigured after his conception.

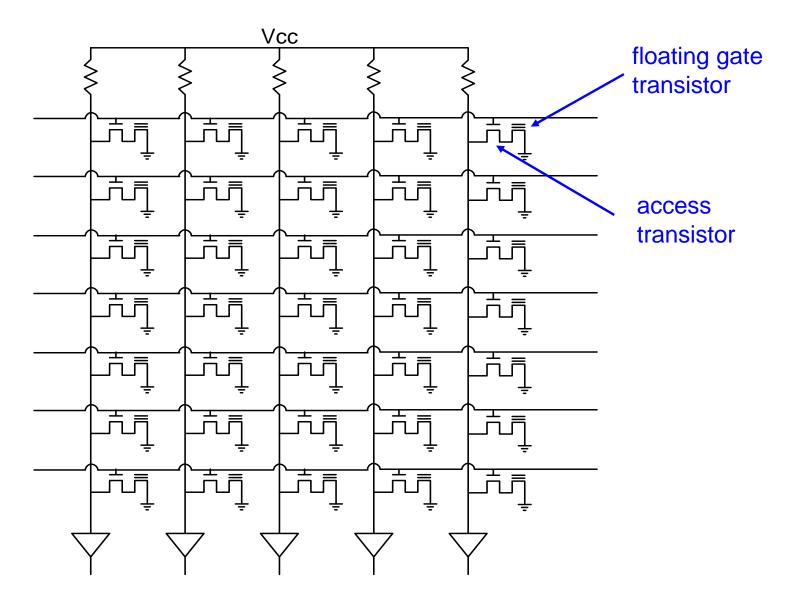

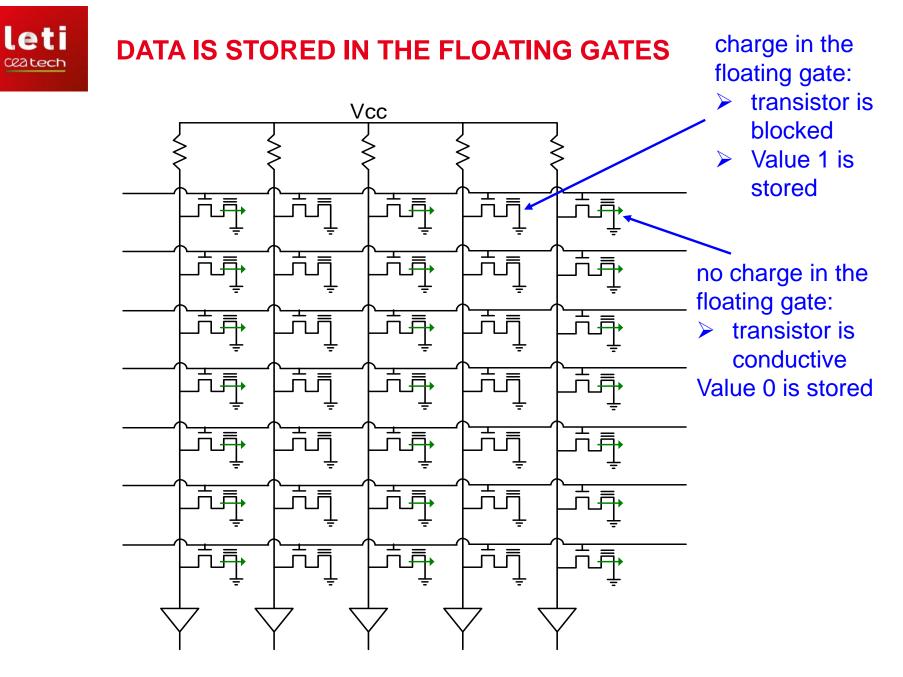

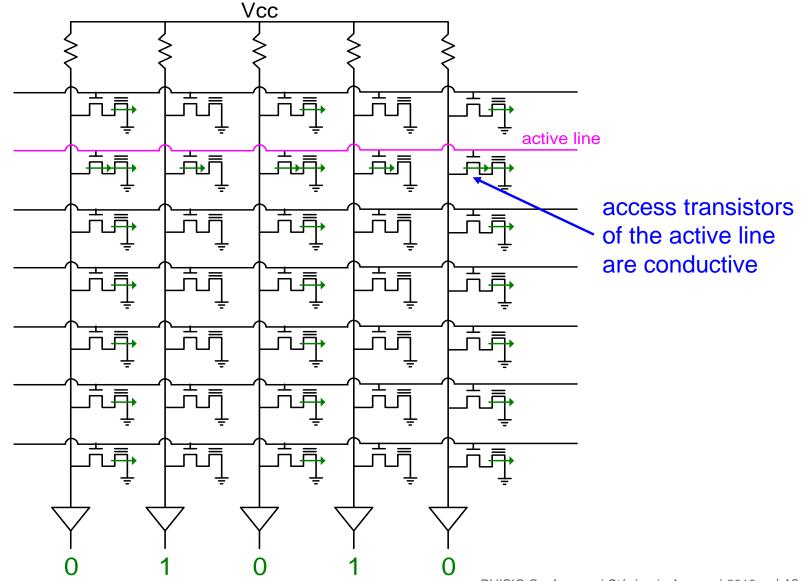

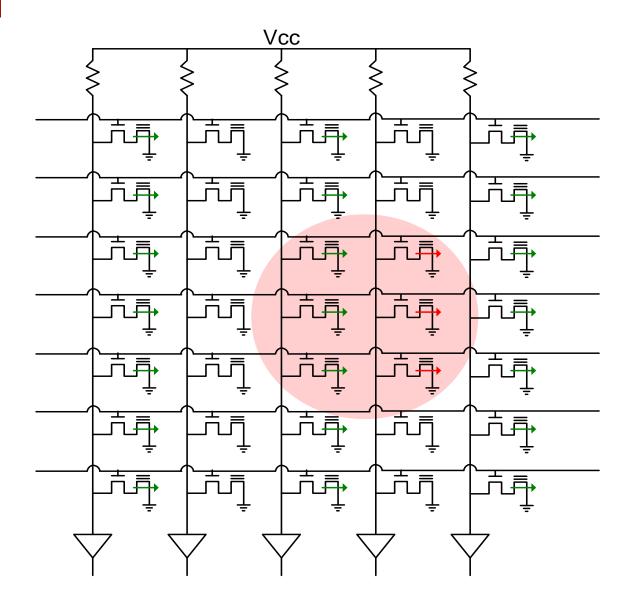

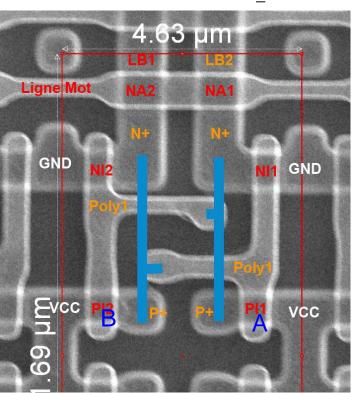

Previous experimentations on ESRF focalized beam line in Grenoble allowed to demonstrate that a focalized XRays perturbation changes the state of a single NMOS transistor and a single memory cell of SRAM-EEPROM and Flash memories block in a semi-permanent manner in the electronic device. This proof of concept has been realized on a new CMOS technology device (45 nm). The 50 nm focalization allows to modify one single NMOS transistor. The most aggressive technologies (<20nm) can be addressed with this technique even with a 50nm focalization diameter. Contrary to the FIB the interconnections of the device are not modified: the state of one (or several if necessary) transistor(s) is modified. This modification is semi-permanent because it is reversible with a simple heating treatment. This new circuit edit technique is very promising.

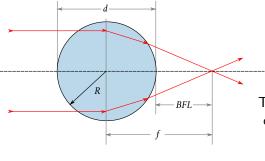

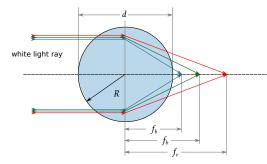

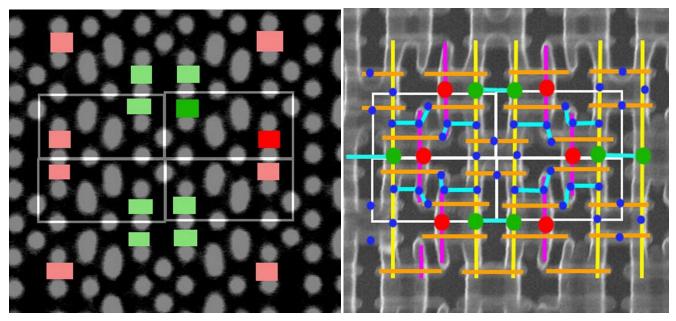

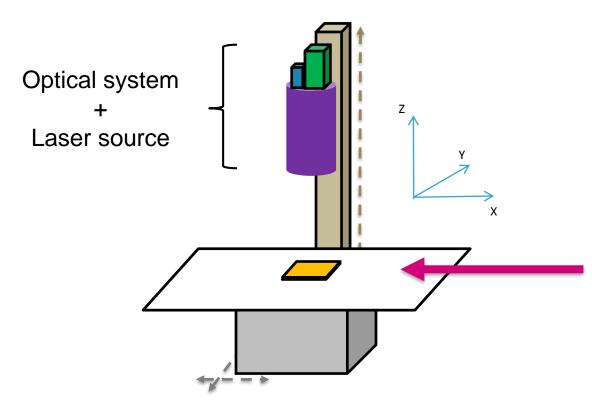

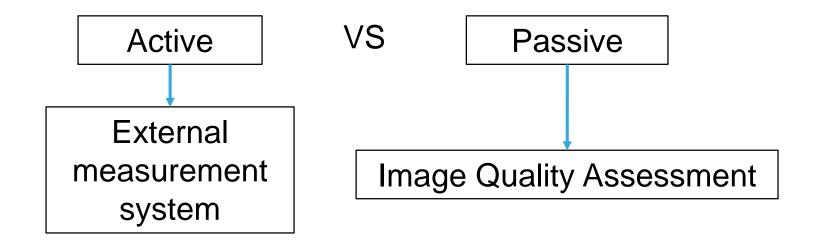

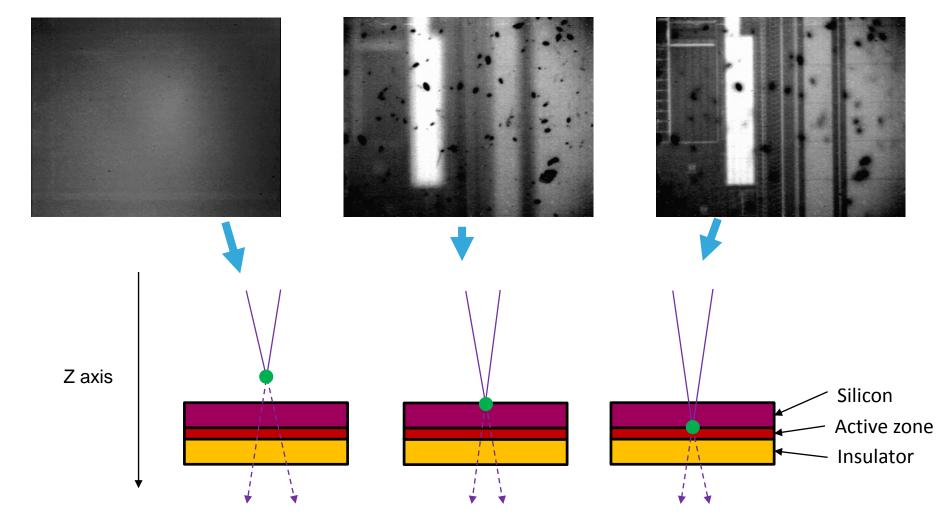

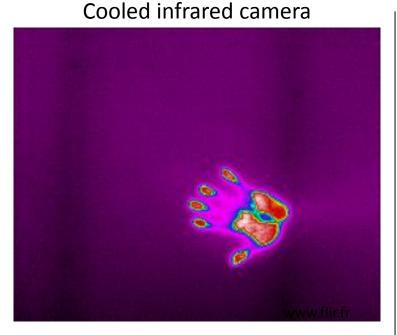

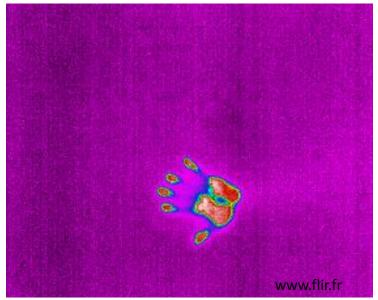

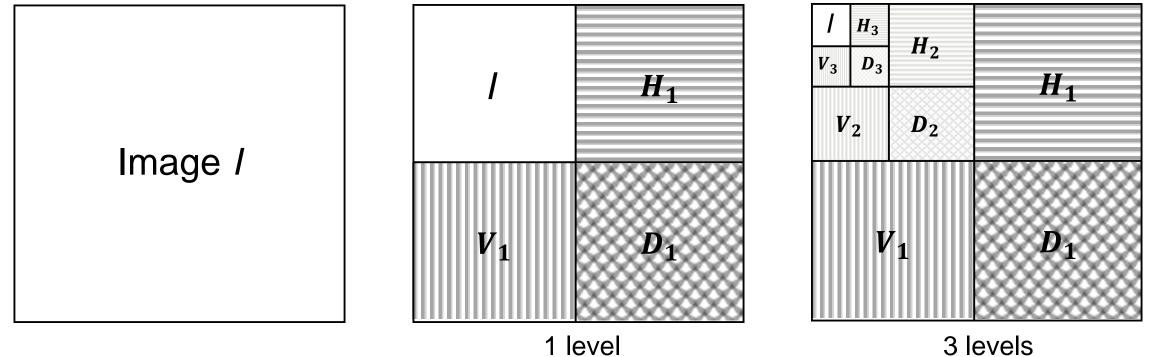

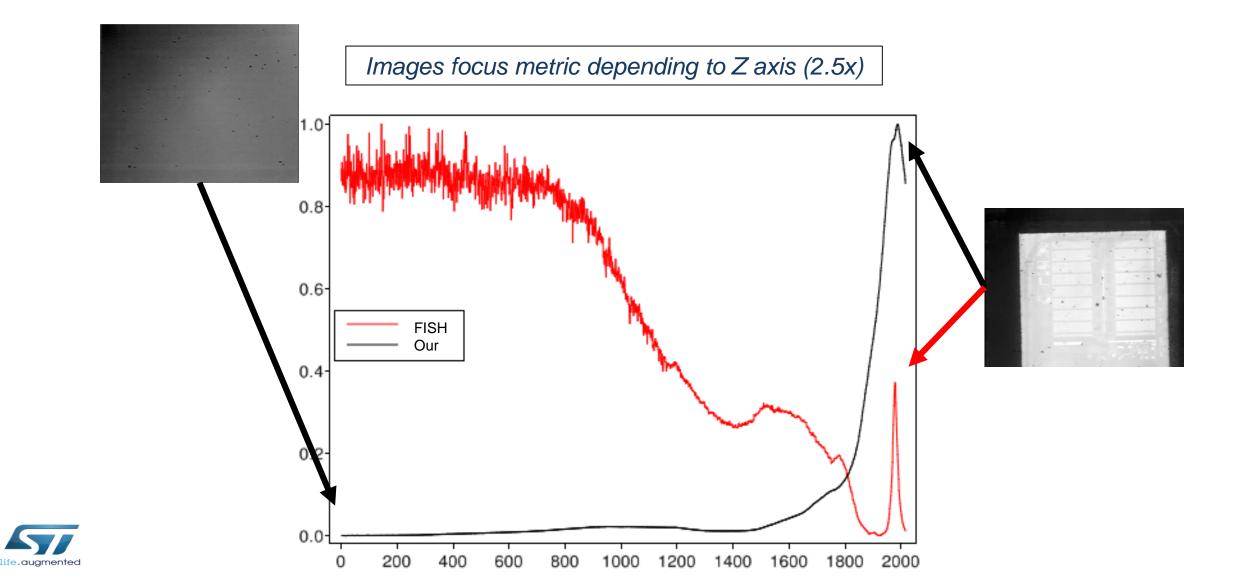

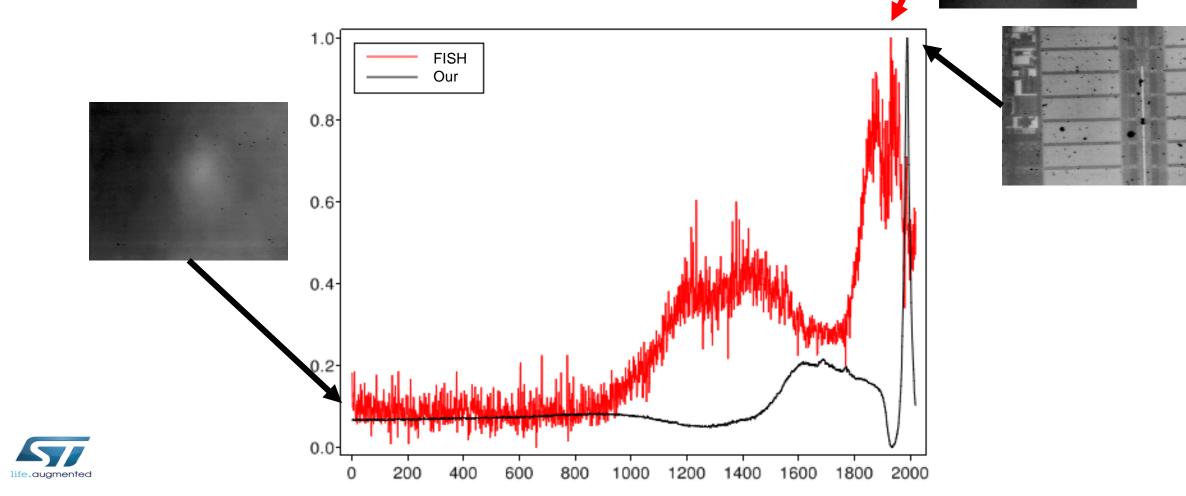

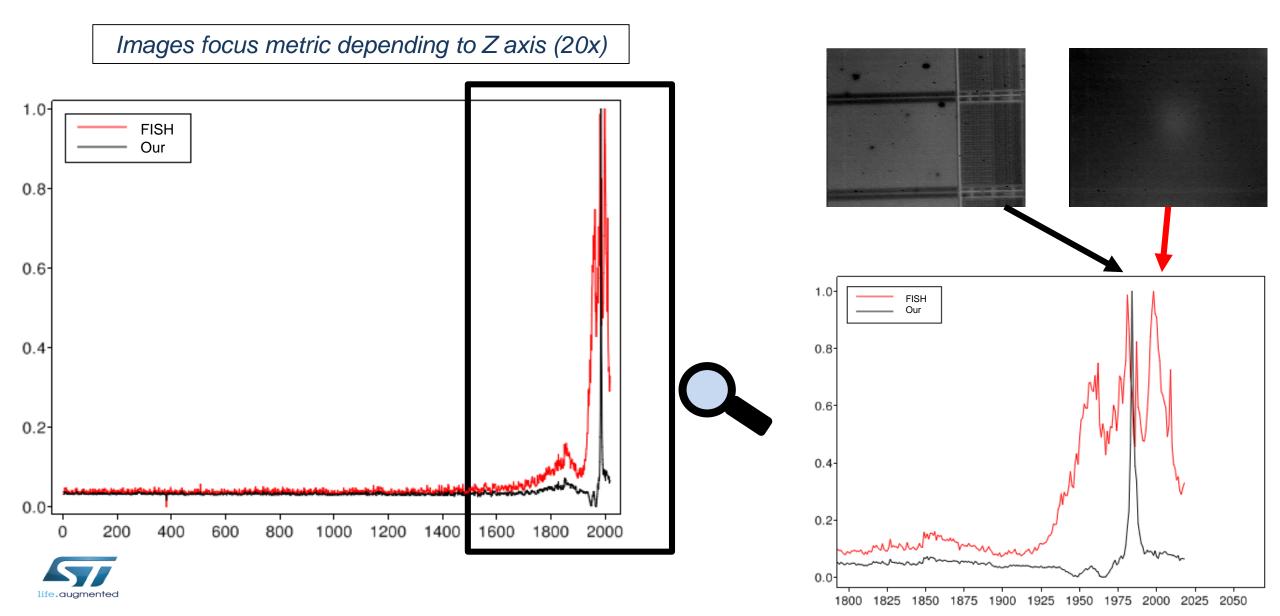

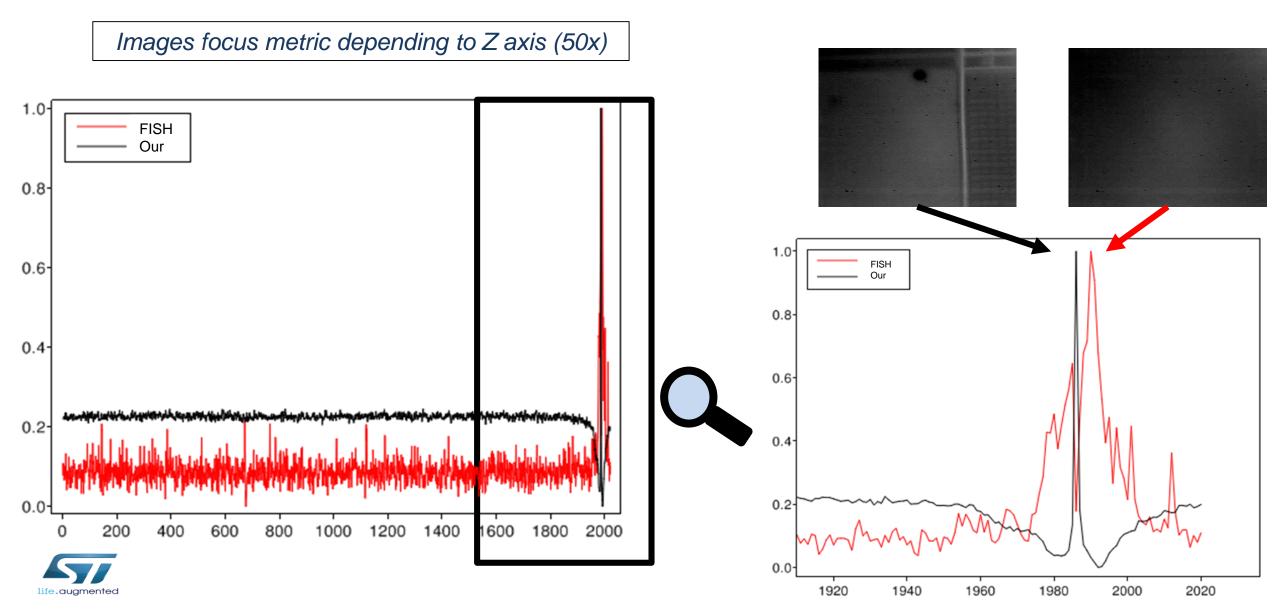

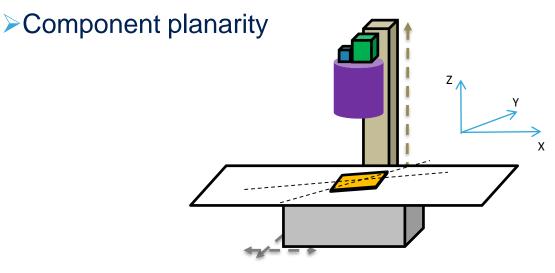

## 5. AUTOFOCUS IN INFRARED MICROSCOPY

## Raphaël Abélé // STMicroelectronics

In the context of the secured Integrated Circuit (IC) characterization, many physical disruptions exists. One of these consists in a laser shot targeted on internal structures of the IC. Accuracy of the shot relies on the precision of the laser power calibration and its 3D positioning inside the IC. An automatic focusing mechanism on the conductive tracks of the IC could help a part of these generally handmade adjustments.

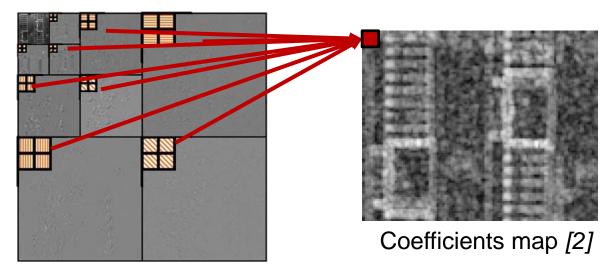

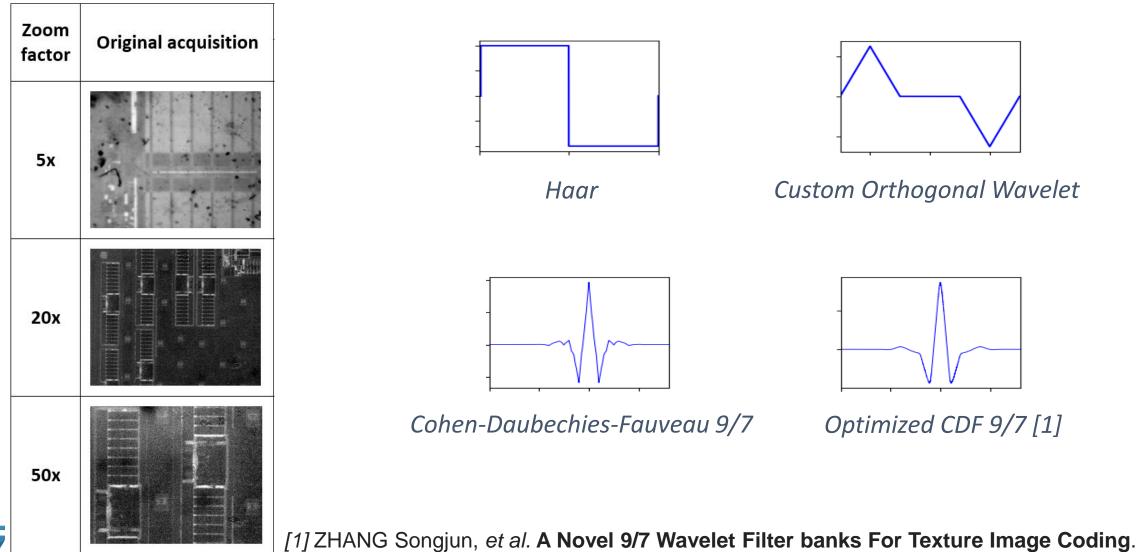

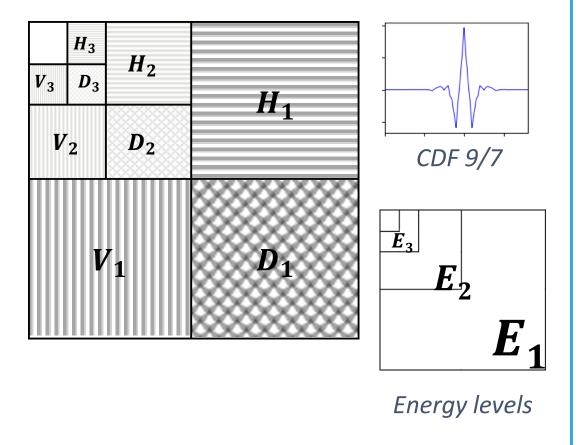

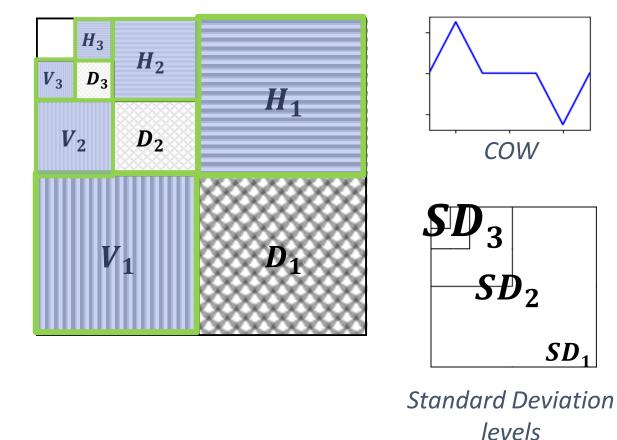

Autofocus (AF) is a widely investigated problem for natural scenes images, industrial assembly and biologic microscopy. A new effective AF method is proposed for infrared (IR) microscopy in the context of Integrated Circuit industry (IC). The proposal operates in the wavelet domain using a custom orthogonal wavelet for the 2D Discrete Wavelet Transform (DWT). The quality criterion of our AF algorithm relies on the standard deviance of the DWT coefficients, computed per subband and per level. Tested on several optical magnifying lenses, our method is robust and time-efficient, usable on the fly in IC location system.

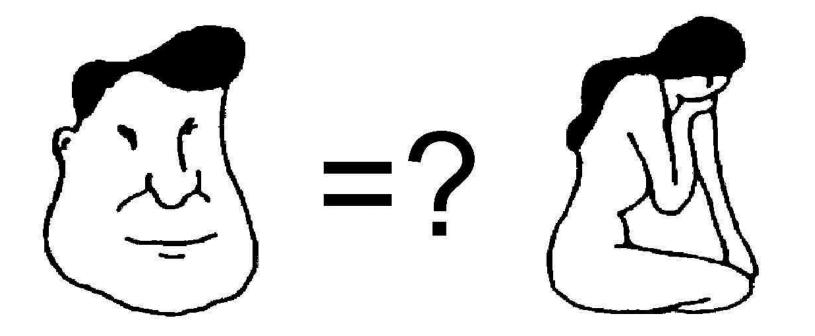

## 6. EVALUATION OF BIOMETRIC SYSTEMS: WHO SAID STRAIGHTFORWARD?

## <u>Claude Barral</u> // Bactec

The current rapid growth of biometric authentication features within consumer devices paves the way to security and performance certification needs. For more than a decade, IT security players tried to map certification schemes from smart cards and ICT systems to the area of Biometrics without success. Why? We will discuss all the issues one may face while setting up an evaluation environment for any biometric systems: which biometric data is targeted? How many different security settings? What is a representative database? Public vs Private databases? Target database size and architecture? How many authentication tests needed to claim a 0,001% false acceptance rate? Which evaluation target: Compliance? Interoperability? Security ? Performances? Well, definitely not straightforward indeed! You will see...

# // SESSION // FAULT INJECTION ANALYSIS: ATTACKS AND PROTECTIONS (II)

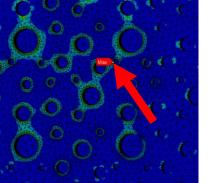

# 7. EM FAULT INJECTION SUSCEPTIBILITY CRITERION AND ITS APPLICATION TO THE LOCALIZATION OF HOTSPOTS

## Maxime Madau // STMicroelectronics / LIRMM

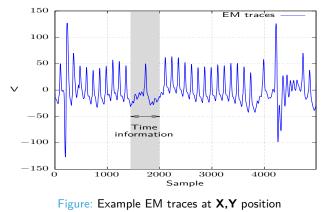

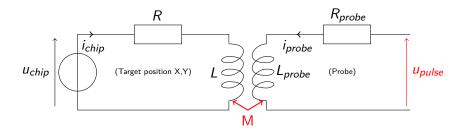

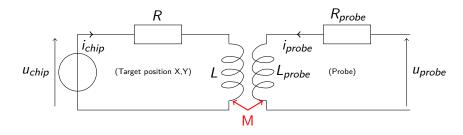

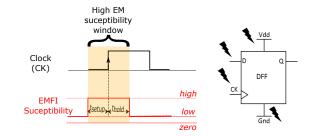

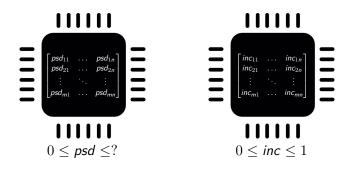

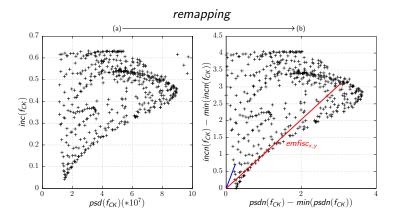

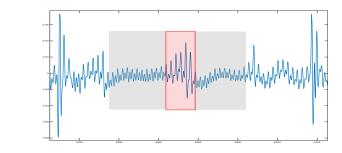

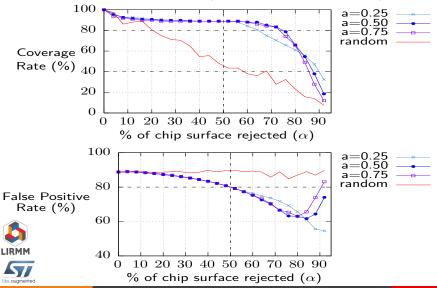

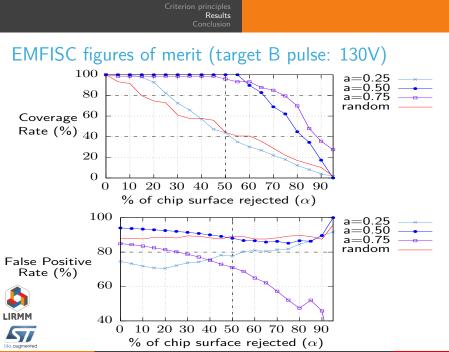

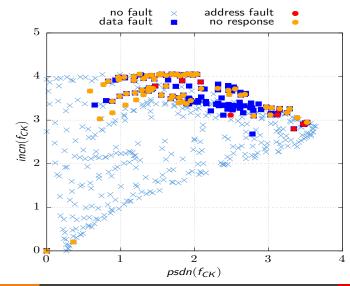

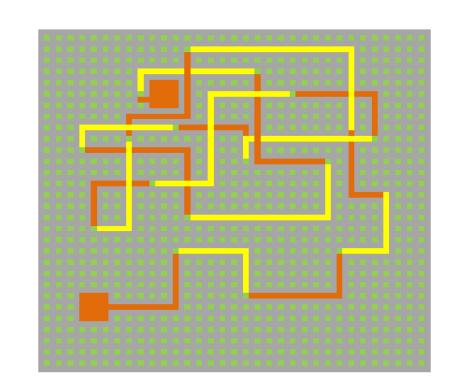

Electromagnetic (EM) fault injection has been proven efficient in attacking targets such as system-onchip (SoC) or smartcards. Nonetheless, security characterizations, performed either by certification laboratories or by firms, are time consuming and this impacts on the final result. Indeed complete tests of integrated circuits (ICs) require trying numerous parameters, from pulse polarity to probes geometry and coupling, hence many maps are required to test all surface of Devices Under Test (DUT) and are unfortunately rarely performed. We propose a criterion to find zones with a high susceptibility to EM Fault Injection (EMFI). By using preprocessing tools based on both the effects of EMFI on circuits and the analysis of EM emission traces, we are able to speed up the search of zones where faults are more likely to occur hence reducing the time required for security characterizations

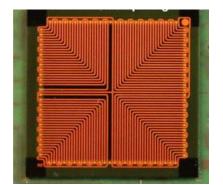

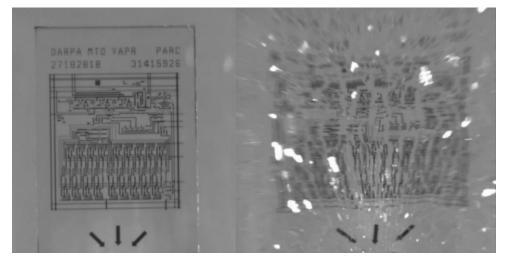

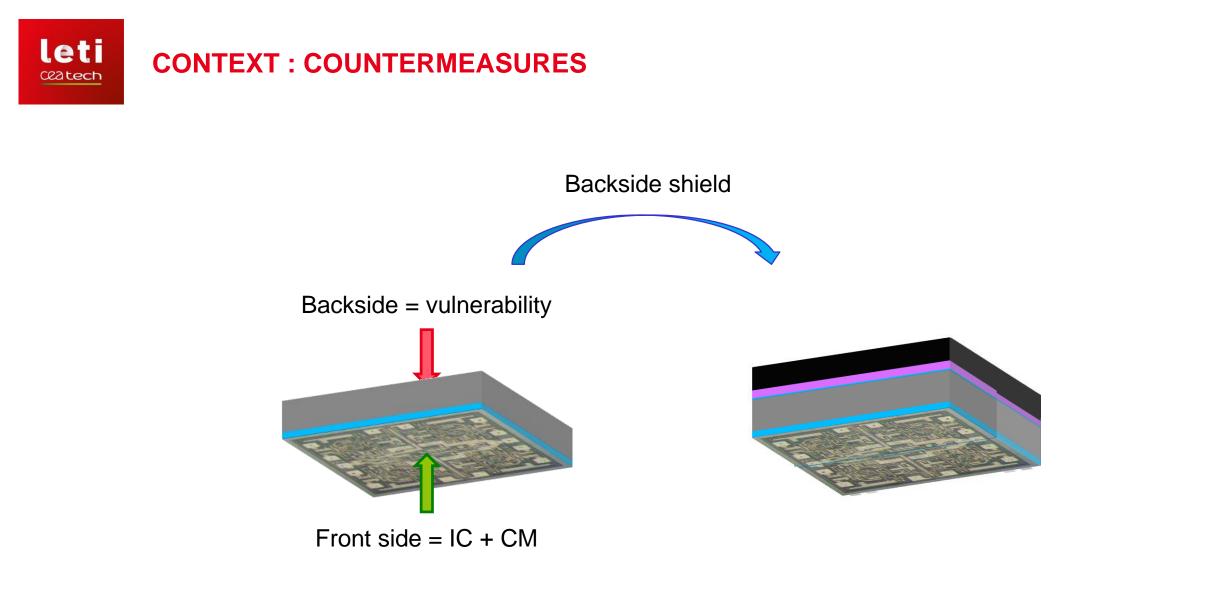

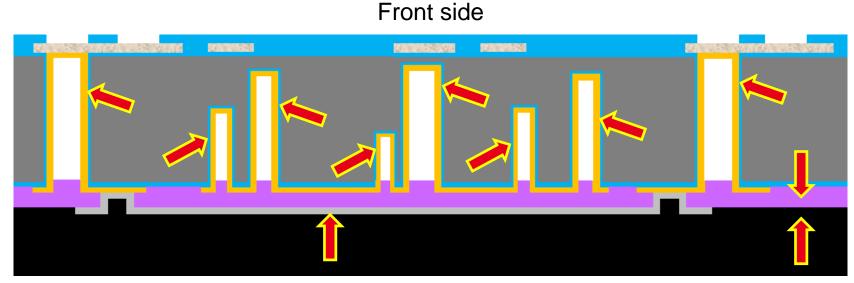

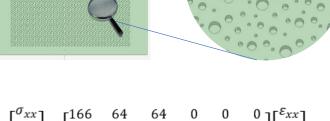

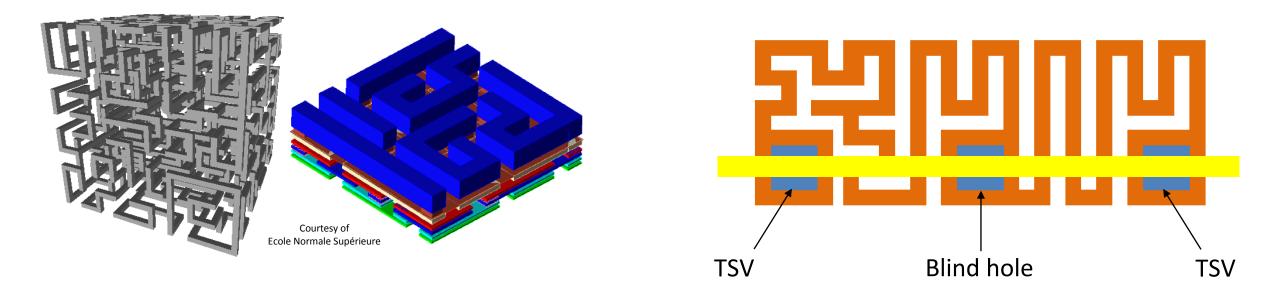

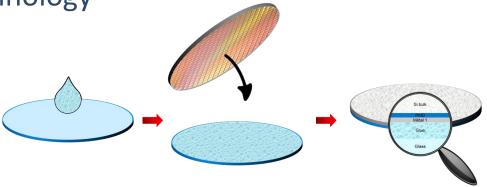

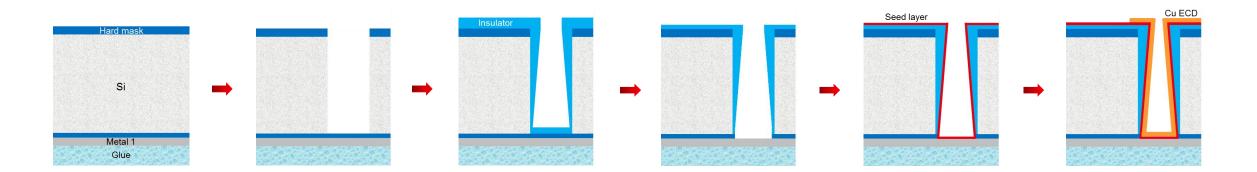

## 8. BACKSIDE SHIELD BASED ON PACKAGING TECHNOLOGIES FOR CHIPS OR SYSTEMS SECURING

# <u>Stephan Borel</u> // CEA Tech

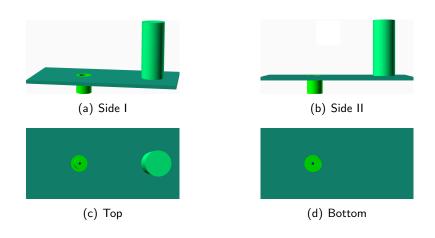

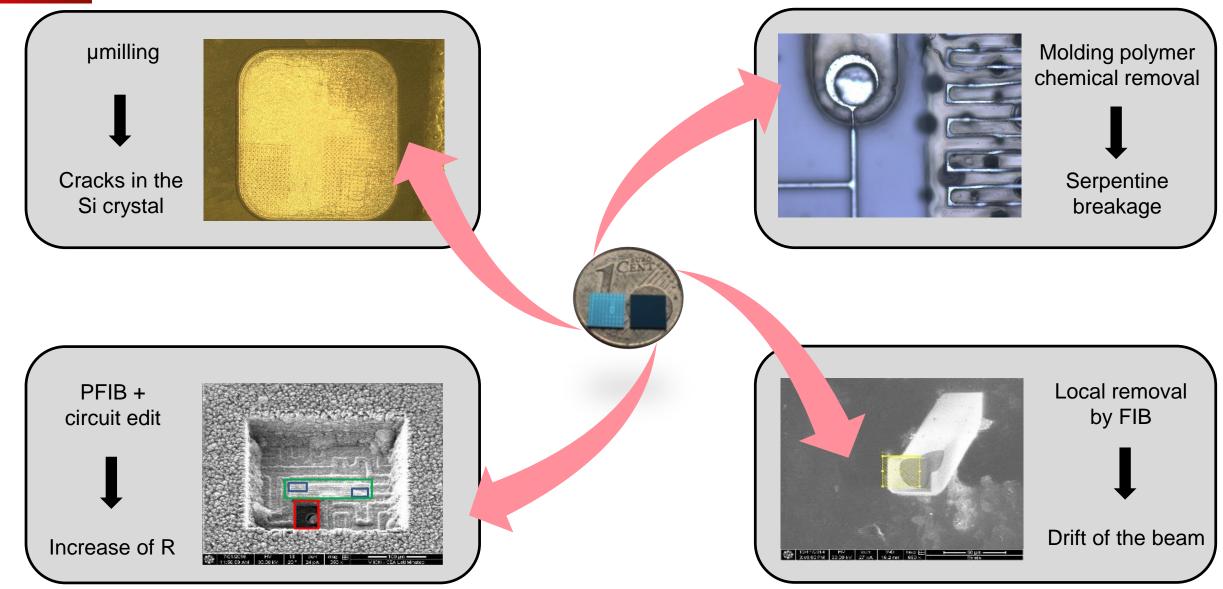

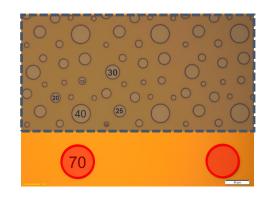

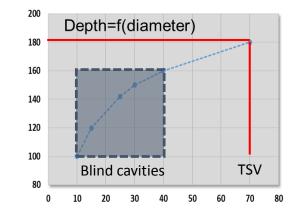

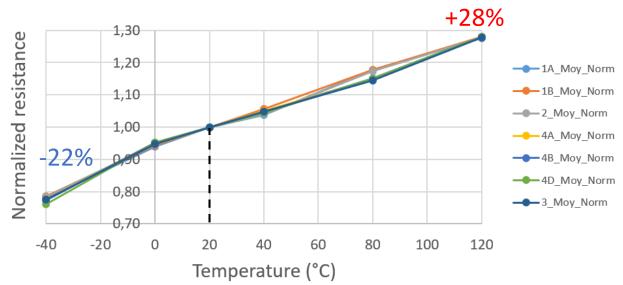

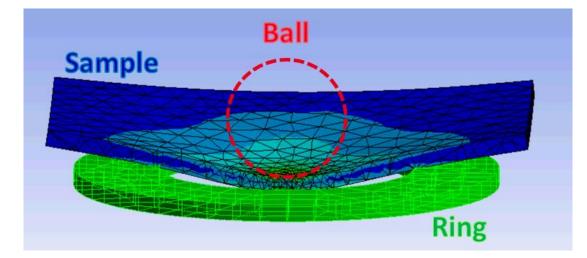

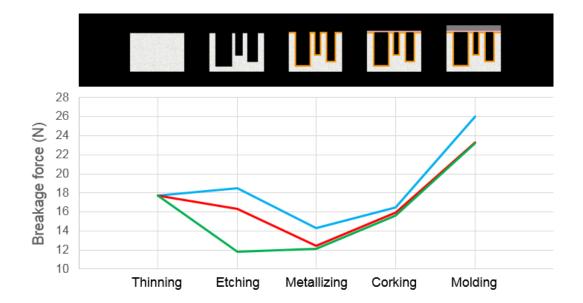

A structure intended to protect Integrated Circuits (IC) against physical attacks will be presented. Located on the backside of a chip, it complements the countermeasures usually available on the front side of secure components. It aims at preventing attacks such as fault injection by laser illumination and can trigger an alert in case of invasive attacks by circuit edit or micro-probing. Weakening structures have been designed so as to cause the breakage of the die in case of thinning, and a metallic serpentine used as an attack witness has been thought with a maximal complexity so that an attacker cannot skirt it. These elements can be fabricated using standard packaging techniques in a wafer level integration, whether at chip or system scale. The concept of a secure System in Package (SiP) using unsecured chips is proposed, opening the perspective of components fully "secured by packaging".

Emmanuel Prouff Joint work with Ryad Benadjila, Eleonora Cagli (CEA LETI), Cécile Dumas (CEA LETI), Houssem Maghrebi (UL), Thibault Portigliatti (ex SAFRAN), Rémi Strullu and Adrian Thillard

> Laboratoire de Sécurité des Composants, ANSSI, France Partially funded by **REASSURE** H2020 Project

> > May, PHYSIC 2018

## Contents

- 1. Context and Motivation

- 1.1 Illustration

- 1.2 Template Attacks

- 1.3 Countermeasures

- 1.4 State of the Art

#### 2. A machine learning approach to classification

- 2.1 Introduction

- 2.2 The Underlying Classification Problem

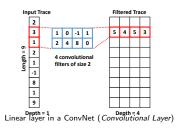

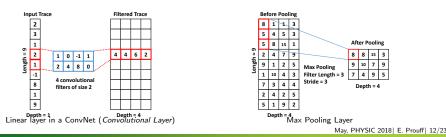

- 2.3 Convolutional Neural Networks

- 2.4 Training of Models

#### 3. Building a Community Around The Subject

- 3.1 ASCAD Open Data-Base

- 3.2 Leakage Characterization and Training

- 3.3 Results

#### 4. Conclusions

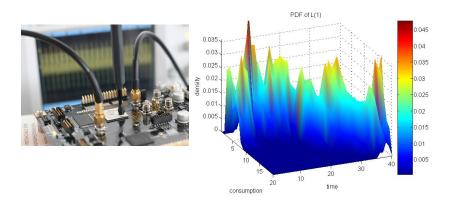

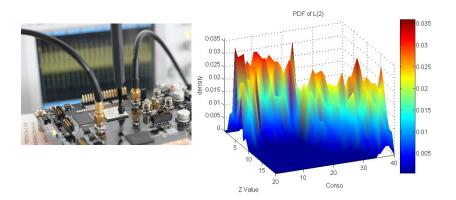

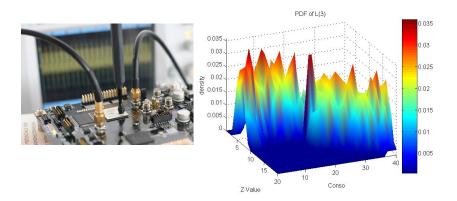

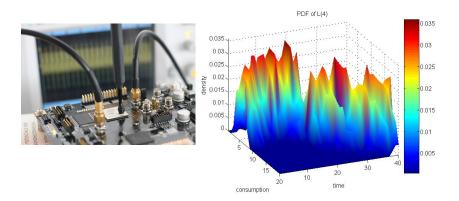

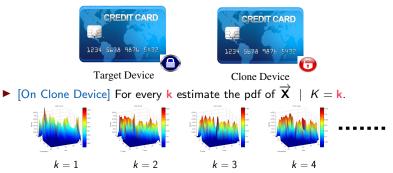

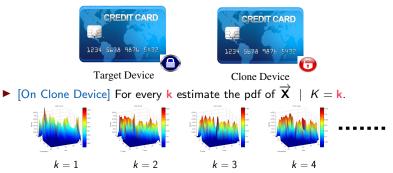

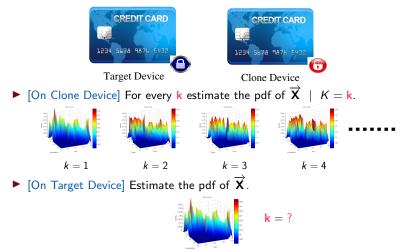

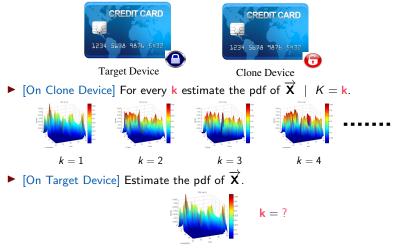

## Probability distribution function (pdf) of Electromagnetic Emanations

Cryptographic Processing with a secret k = 1.

Cryptographic Processing with a secret k = 1.

Cryptographic Processing with a secret k = 2.

Cryptographic Processing with a secret k = 3.

Cryptographic Processing with a secret k = 4.

#### Context:

A

#### Context:

#### Context:

#### Context:

#### Context:

► [Key-recovery] Compare the pdf estimations.

May, PHYSIC 2018 E. Prouff 4/23

#### Notations

- $\vec{X}$  observation of the device behaviour

- P public input of the processing

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

#### Notations

- $\vec{X}$  observation of the device behaviour

- P public input of the processing

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

$\Pr[\mathbf{Z}|\vec{\mathbf{X}}]$

- $\vec{X}$  observation of the device behaviour

- P public input of the processing

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

#### Template Attacks

Profiling phase (using profiling traces under known Z)

• Attack phase (*N* attack traces  $\vec{x}_i$ , e.g. with known plaintexts  $p_i$ )

$\Pr[\mathbf{Z}|\mathbf{X}]$

#### Notations

- $\vec{X}$  observation of the device behaviour

- P public input of the processing

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

## Template Attacks

Profiling phase (using profiling traces under known Z)

estimate Pr[X|Z = z] by simple distributions for each value of z

Attack phase (N attack traces x<sub>i</sub>, e.g. with known plaintexts p<sub>i</sub>)

#### Notations

- $\vec{X}$  observation of the device behaviour

- P public input of the processing

- ▶ **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

## Template Attacks

- Profiling phase (using profiling traces under known Z)

- estimate  $\Pr[\vec{X}|Z = z]$  for each value of z

- Attack phase (N attack traces  $\vec{x}_i$ , e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log \Pr[\vec{\mathbf{X}} = \vec{\mathbf{x}}_i | Z = f(p_i, k)]$$

#### Notations

- $\vec{X}$  observation of the device behaviour

- P public input of the processing

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

#### Template Attacks

- Profiling phase (using profiling traces under known Z)

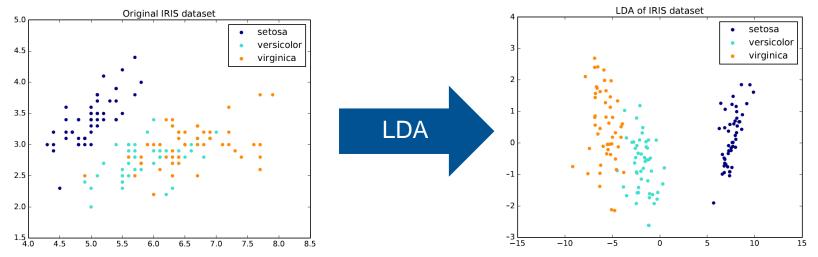

- mandatory dimensionality reduction

- estimate  $\Pr[\vec{X}|Z = z]$  for each value of z

- Attack phase (N attack traces  $\vec{x}_i$ , e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log \Pr[\vec{\mathbf{X}} = \vec{\mathbf{x}}_i | Z = f(p_i, k)]$$

#### Notations

- $\vec{X}$  observation of the device behaviour

- P public input of the processing

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

## Template Attacks

- Profiling phase (using profiling traces under known Z)

- manage de-synchronization problem

- mandatory dimensionality reduction

- estimate  $\Pr[\varepsilon(\tilde{X})|\mathbf{Z} = \mathbf{z}]$  for each value of  $\mathbf{z}$

- Attack phase (*N* attack traces  $\vec{x}_i$ , e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log \Pr[\varepsilon(\tilde{\mathbf{X}}) = \varepsilon(\tilde{\mathbf{x}}_i) | Z = f(p_i, k)]$$

## Defensive Mechanisms

#### Misaligning Countermeasures

- Random Delays, Clock Jittering, ...

- ▶ In theory: assume to be insufficient to provide security

- In practice: one of the main issues for evaluators

- ► ⇒ Need for efficient resynchronization techniques

## Defensive Mechanisms

#### Misaligning Countermeasures

- ▶ Random Delays, Clock Jittering, ...

- ▶ In theory: assume to be insufficient to provide security

- In practice: one of the main issues for evaluators

- $\blacktriangleright \implies \mathsf{Need for efficient resynchronization techniques}$

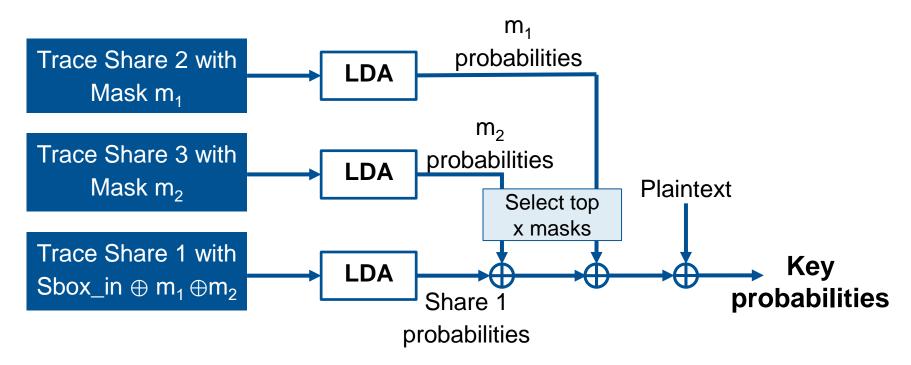

#### Masking Countermeasure

- Each key-dependent internal state element is randomly split into 2 shares

- $\blacktriangleright$  The crypto algorithm is adapted to always manipulate shares at  $\neq$  times

- The adversary needs to recover information on the two shares to recover K

- ► ⇒ Need for efficient Methods to recover tuple of leakage samples that jointly depend on the target secret

## Contents

#### 1. Context and Motivation

- 1.1 Illustration

- 1.2 Template Attacks

- 1.3 Countermeasures

- 1.4 State of the Art

#### 2. A machine learning approach to classification

- 2.1 Introduction

- 2.2 The Underlying Classification Problem

- 2.3 Convolutional Neural Networks

- 2.4 Training of Models

- 3. Building a Community Around The Subject

- 3.1 ASCAD Open Data-Base

- 3.2 Leakage Characterization and Training

- 3.3 Results

#### 4. Conclusions

## Motivating Conclusions

# Motivating Conclusions

#### Now:

- preprocessing to prepare data

- Traces resynchronisation

- Selection of Pols

- make strong hypotheses on the statistical dependency

- e.g. Gaussian approximation

- characterization to extract information

- e.g. Maximum Likelihood

The proposed perspective:

- preprocessing to prepare data

- Traces resynchronisation

- Selection of Pols

- make strong hypotheses on the statistical dependency

- e.g. Gaussian approximation

- Train algorithms to directly extract information

# Side Channel Attacks

#### Notations

- ► X side channel trace

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

Pr[Z|X

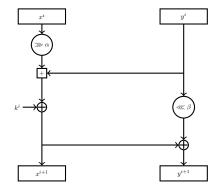

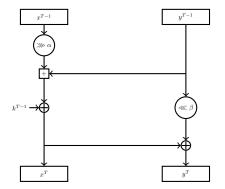

## Template-Attacks Machine Learning Side Channel Attacks

- Profiling phase (using profiling traces under known Z)

- manage de-synchronization problem

- mandatory dimensionality reduction

- estimate  $\Pr[\vec{X}|Z = z]$  for each value of z

- Attack phase (N attack traces, e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log \Pr[\vec{\mathbf{X}} = \vec{\mathbf{x}}_i | Z = f(p_i, k)]$$

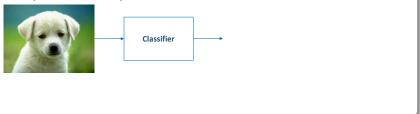

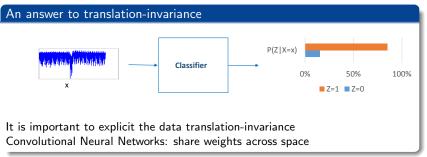

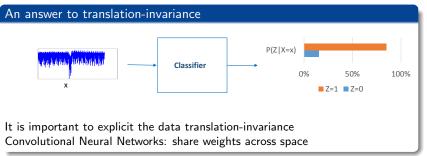

# Side Channel Attacks with a Classifier

#### Notations

- ► X side channel trace

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

Pr[Z|X

## Template-Attacks Machine Learning Side Channel Attacks

- Profiling phase (using profiling traces under known Z)

- manage de-synchronization problem

- mandatory dimensionality reduction

- estimate  $\Pr[\vec{X}|Z = z]$  for each value of z

- Attack phase (N attack traces, e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log \Pr[\vec{\mathbf{X}} = \vec{\mathbf{x}}_i | Z = f(p_i, k)]$$

#### Notations

- ► X side channel trace

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

Pr[Z|X

#### Template-Attacks Machine Learning Side Channel Attacks

Training phase (using training traces under known Z)

- manage de-synchronization problem

- mandatory dimensionality reduction

- estimate  $\Pr[\vec{X}|Z = z]$  for each value of z

- Attack phase (N attack traces, e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log \Pr[\vec{\mathbf{X}} = \vec{\mathbf{x}}_i | Z = f(p_i, k)]$$

#### Notations

- ► X side channel trace

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

Pr[Z|X

#### Template-Attacks Machine Learning Side Channel Attacks

Training phase (using training traces under known Z)

- manage de-synchronization problem

- mandatory dimensionality reduction

- construct a classifier F s.t.  $F(\vec{x})[z] = y \approx \Pr[Z = z | \vec{X} = \vec{x}]$

- Attack phase (N attack traces, e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log \Pr[\vec{\mathbf{X}} = \vec{\mathbf{x}}_i | Z = f(p_i, k)]$$

#### Notations

- ► X side channel trace

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

Pr[Z|X

#### Template-Attacks Machine Learning Side Channel Attacks

Training phase (using training traces under known Z)

- manage de-synchronization problem

- mandatory dimensionality reduction

- construct a classifier F s.t.  $F(\vec{x})[z] = y \approx \Pr[Z = z | \vec{X} = \vec{x}]$

- Attack phase (N attack traces, e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log F(\vec{\mathbf{x}}_i)[f(p_i, k)]$$

#### Notations

- ► X side channel trace

- **Z** target (a cryptographic sensitive variable  $\mathbf{Z} = f(P, K)$ )

Goal: make inference over Z, observing  $\vec{X}$

#### Template Attacks Machine Learning Side Channel Attacks

Training phase (using training traces under known Z)

- manage de-synchronization problem

- mandatory dimensionality reduction

- construct a classifier F s.t.  $F(\vec{x})[z] = y \approx \Pr[Z = z | \vec{X} = \vec{x}]$

Integrated approach

- Attack phase (N attack traces, e.g. with known plaintexts  $p_i$ )

- Log-likelihood score for each key hypothesis k

$$d_k = \sum_{i=1}^N \log F(\vec{\mathbf{x}}_i)[f(p_i, k)]$$

Pr[Z]

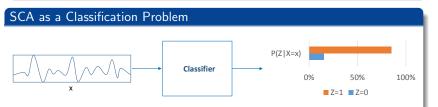

#### Classification problem

#### Classification problem

#### Classification problem

#### Classification problem

#### Overview of Machine Learning Methodology

Human effort:

- choose a class of algorithms

- choose a model to fit + tune hyper-parameters

Automatic training:

automatic tuning of trainable parameters to fit data

#### Overview of Machine Learning Methodology

Human effort:

- choose a class of algorithms Neural Networks

- choose a model to fit + tune hyper-parameters

Automatic training:

automatic tuning of trainable parameters to fit data

Stochastic Gradient Descent

#### Overview of Machine Learning Methodology

Human effort:

- choose a class of algorithms Neural Networks

- choose a model to fit + tune hyper-parameters MLP, ConvNet

Automatic training:

automatic tuning of trainable parameters to fit data

Stochastic Gradient Descent

#### Overview of Machine Learning Methodology

Human effort:

- choose a class of algorithms Neural Networks

- choose a model to fit + tune hyper-parameters MLP, ConvNet

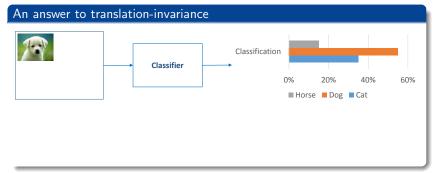

Automatic training:

automatic tuning of trainable parameters to fit data Stochastic Gradient Descent

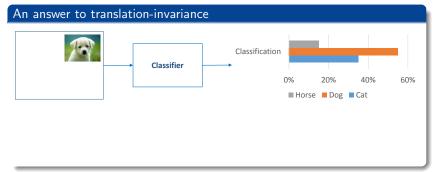

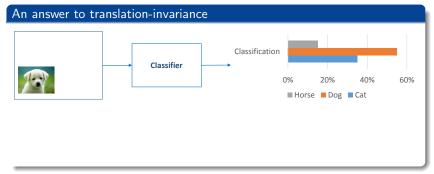

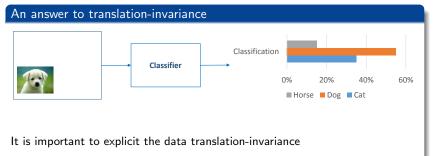

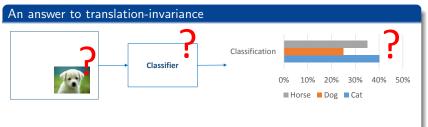

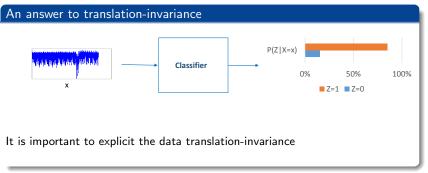

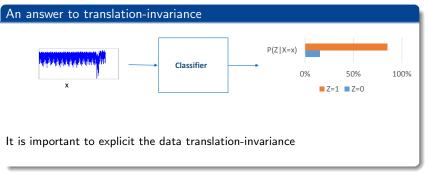

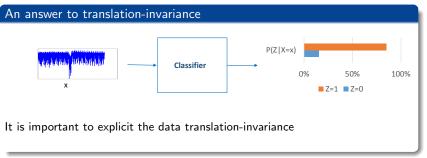

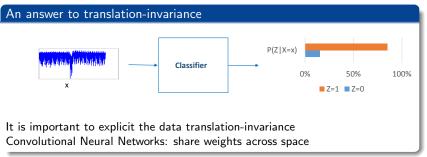

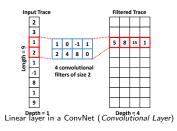

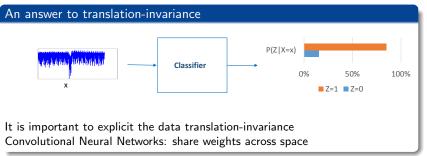

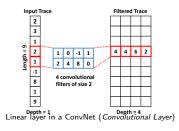

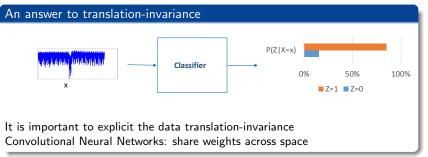

It is important to explicit the data translation-invariance

Trading Side-Channel Expertise for Deep Learning Expertise .... or huge computational power!

Training

Trading Side-Channel Expertise for Deep Learning Expertise .... or huge computational power!

#### Training

Aims at finding the **parameters** of the function modelling for the dependency btw the target value and the leakage.

Trading Side-Channel Expertise for Deep Learning Expertise .... or huge computational power!

#### Training

Aims at finding the **parameters** of the function modelling for the dependency btw the target value and the leakage.

The search is done by solving a minimization problem with respect to some metric (aka loss function)

Trading Side-Channel Expertise for Deep Learning Expertise .... or huge computational power!

#### Training

Aims at finding the **parameters** of the function modelling for the dependency btw the target value and the leakage.

The search is done by solving a minimization problem with respect to some metric (aka loss function)

The training algorithm has itself some training hyper-parameters: the number of iterations (aka epochs) of the minimization procedure, the number of input traces (aka batch) treated during a single iteration.

Trading Side-Channel Expertise for Deep Learning Expertise .... or huge computational power!

#### Training

Aims at finding the **parameters** of the function modelling for the dependency btw the target value and the leakage.

The search is done by solving a minimization problem with respect to some metric (aka loss function)

The training algorithm has itself some training hyper-parameters: the number of iterations (aka epochs) of the minimization procedure, the number of input traces (aka batch) treated during a single iteration.

The trained model has architecture hyper-parameters:

the size of the layers, the nature of the layers, the number of layers, etc.

Trading Side-Channel Expertise for Deep Learning Expertise .... or huge computational power!

#### Training

Aims at finding the **parameters** of the function modelling for the dependency btw the target value and the leakage.

The search is done by solving a minimization problem with respect to some metric (aka loss function)

The training algorithm has itself some training hyper-parameters: the number of iterations (aka epochs) of the minimization procedure, the number of input traces (aka batch) treated during a single iteration.

The trained model has architecture hyper-parameters:

the size of the layers, the nature of the layers, the number of layers, etc.

#### Tricky Points

Find sound hyper-parameters is the main issue in Deep Learning: this can be done thanks to a good understanding of the underlying structure of the data and/or access to important computational power.

### Contents

#### 1. Context and Motivation

- 1.1 Illustration

- 1.2 Template Attacks

- 1.3 Countermeasures

- 1.4 State of the Art

#### 2. A machine learning approach to classification

- 2.1 Introduction

- 2.2 The Underlying Classification Problem

- 2.3 Convolutional Neural Networks

- 2.4 Training of Models

- 3. Building a Community Around The Subject

- 3.1 ASCAD Open Data-Base

- 3.2 Leakage Characterization and Training

- 3.3 Results

#### 4. Conclusions

# Creation of an open database for Training and Testing

#### ANSSI recently publishes

- source codes of secure implementations of AES128 for public 8-bit architectures (https://github.com/ANSSI-FR/secAES-ATmega8515)

- first version: 10-masking + processing in random order

- second version: affine masking + processing in random order (plus other minor tricks)

- data-bases of electromagnetic leakages (https://github.com/ANSSI-FR/ASCAD)

- example scripts for the training and testing of models in SCA contexts

#### Goal

- Enable fair and easy benchmarking

- Initiate discussions and exchanges on the application of DL to SCA

- Create a community of contributors on this subject

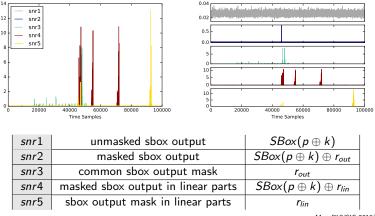

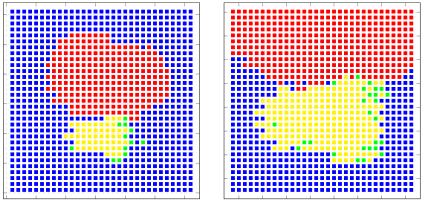

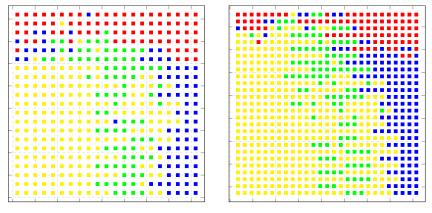

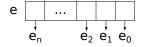

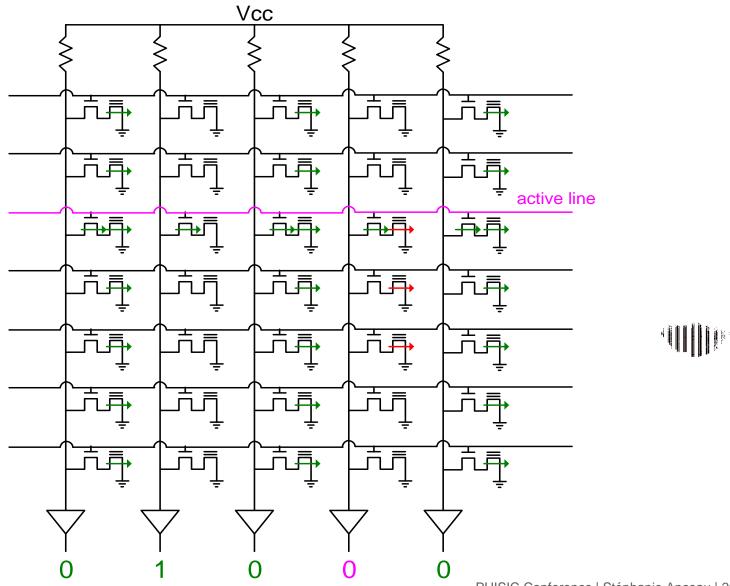

### Nature of the Observations/Traces

Side-channel observations in ASCAD correspond to the masked processing of a simple cryptographic primitive Information leakage validated thanks to SNR characterization

### Nature of the Observations/Traces

Side-channel observations in ASCAD correspond to the masked processing of a simple cryptographic primitive

Information leakage validated thanks to SNR characterization

May, PHYSIC 2018 | E. Prouff | 16/23

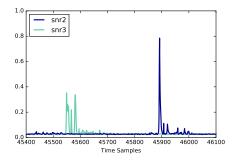

#### Nature of the Observations/Traces

Side-channel observations in ASCAD correspond to the masked processing of a simple cryptographic primitive

Information leakage validated thanks to SNR characterization

Validate that shares are manipulated at different times

#### Nature of the Observations/Traces

Side-channel observations in ASCAD correspond to the masked processing of a simple cryptographic primitive

Information leakage validated thanks to SNR characterization

Validate that shares are manipulated at different times Scripts are also proposed to add artificial signal jittering

#### Our Training Strategy

#### Our Training Strategy

Find a **base model architecture** and find training hyper-parameters for which a convergence towards the good key hypothesis is visible

#### Our Training Strategy

Find a base model architecture and find training hyper-parameters for which a convergence towards the good key hypothesis is visible Fine-tune all the hyper-parameters one after another to get the best efficiency/effectiveness trade-off

#### Our Training Strategy

Find a base model architecture and find training hyper-parameters for which a convergence towards the good key hypothesis is visible Fine-tune all the hyper-parameters one after another to get the best efficiency/effectiveness trade-off

| Parameter               | Reference              | Metric                        | Range                              | Choice    |

|-------------------------|------------------------|-------------------------------|------------------------------------|-----------|

| Training Parameters     |                        |                               |                                    |           |

| Epochs                  | -                      | rank <i>vs</i> time           | $10, 25, 50, 60, \ldots, 100, 150$ | up to 100 |

| Batch Size              | -                      | rank <i>vs</i> time           | 50, 100, 200                       | 200       |

| Architecture Parameters |                        |                               |                                    |           |

| Blocks                  | n <sub>blocks</sub>    | rank, accuracy                | [25]                               | 5         |

| CONV layers             | n <sub>conv</sub>      | rank, accuracy                | [03]                               | 1         |

| Filters                 | n <sub>filters,1</sub> | rank <i>vs</i> time           | $\{2^i; i \in [47]\}$              | 64        |

| Kernel Size             | -                      | rank                          | $\{3, 6, 11\}$                     | 11        |

| FC Layers               | n <sub>dense</sub>     | rank, accuracy <i>vs</i> time | [03]                               | 2         |

| ACT Function            | α                      | rank                          | ReLU, Sigmoid, Tanh                | ReLU      |

| Pooling Layer           | -                      | rank                          | Max, Average, Stride               | Average   |

| Padding                 | -                      | rank                          | Same, Valid                        | Same      |

#### Table: Benchmarks Summary

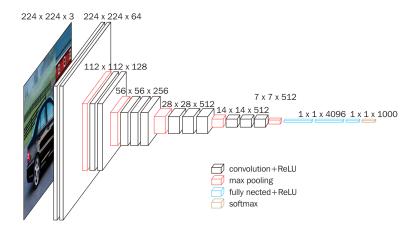

#### The Base Architecture

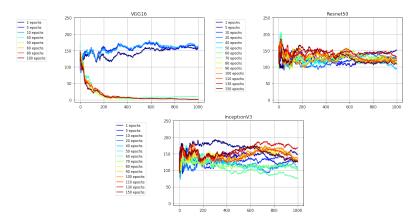

h Mean rank of the good-key hypothesis obtained with VGG-16, ResNet-50 and Inception-v3 w.r.t. different epochs:

#### VGG-16 Architecture

May, PHYSIC 2018 | E. Prouff | 19/23

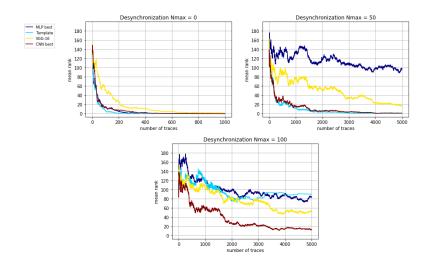

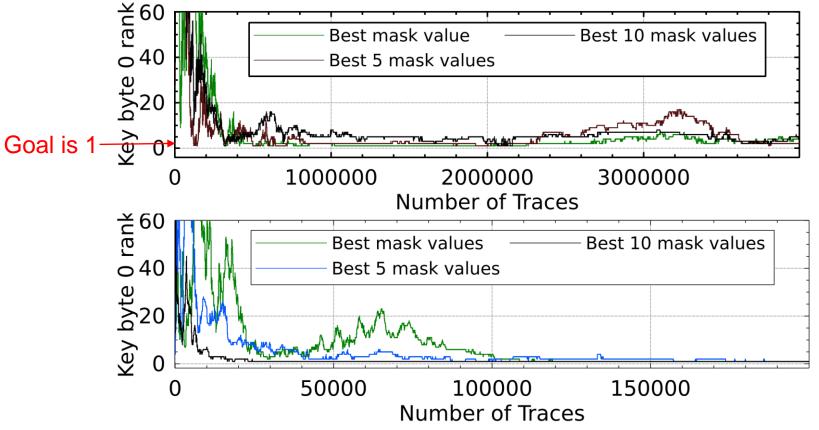

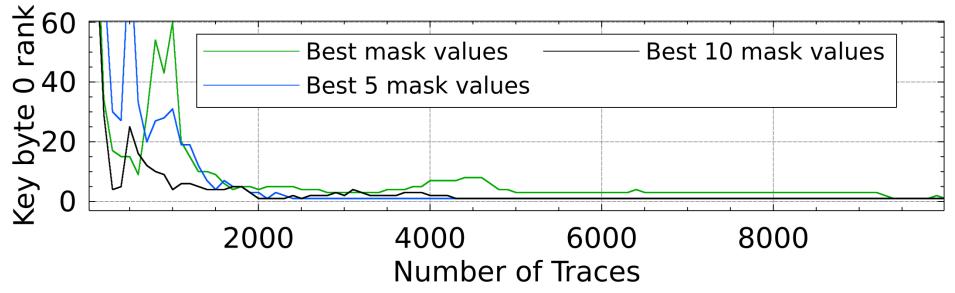

#### Comparisons with State-Of-the-Art Methods

#### Feedbacks & Open Issues

#### Feedbacks

▶ The number of epochs for the training is between 100 and 1000

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- Data-bases for the training must be large

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- Data-bases for the training must be large

- Require important processing capacities (several GPUs, RAM memory, etc.)

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- Data-bases for the training must be large

- Require important processing capacities (several GPUs, RAM memory, etc.)

- Importance of cross-validation

#### Feedbacks

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- Data-bases for the training must be large

- Require important processing capacities (several GPUs, RAM memory, etc.)

- Importance of cross-validation

#### **Open Issues**

#### Feedbacks

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- Data-bases for the training must be large

- Require important processing capacities (several GPUs, RAM memory, etc.)

- Importance of cross-validation

#### **Open** Issues

Models are trained to recover manipulated values (*e.g.* sbox outputs) but not the key itself

#### Feedbacks

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- Data-bases for the training must be large

- Require important processing capacities (several GPUs, RAM memory, etc.)

- Importance of cross-validation

#### **Open Issues**

- Models are trained to recover manipulated values (*e.g.* sbox outputs) but not the key itself

- Current loss functions measure the accuracy of pdf estimations but not the efficiency of the resulting attack

#### Feedbacks

- ▶ The number of epochs for the training is between 100 and 1000

- Model architectures are relatively complex (more than 10 layers)

- Data-bases for the training must be large

- Require important processing capacities (several GPUs, RAM memory, etc.)

- Importance of cross-validation

#### **Open** Issues

- Models are trained to recover manipulated values (*e.g.* sbox outputs) but not the key itself

- Current loss functions measure the accuracy of pdf estimations but not the efficiency of the resulting attack

- Adaptation to get (very) efficient key enumeration algorithms

#### Contents

#### 1. Context and Motivation

- 1.1 Illustration

- 1.2 Template Attacks

- 1.3 Countermeasures

- 1.4 State of the Art

#### 2. A machine learning approach to classification

- 2.1 Introduction

- 2.2 The Underlying Classification Problem

- 2.3 Convolutional Neural Networks

- 2.4 Training of Models

#### 3. Building a Community Around The Subject

- 3.1 ASCAD Open Data-Base

- 3.2 Leakage Characterization and Training

- 3.3 Results

#### Conclusions

State-of-the-Art Template Attack separates resynchronization/dimensionality reduction from characterization

- State-of-the-Art Template Attack separates resynchronization/dimensionality reduction from characterization

- Deep Learning provides an integrated approach to directly extract information from rough data (no preprocessing)

- State-of-the-Art Template Attack separates resynchronization/dimensionality reduction from characterization

- Deep Learning provides an integrated approach to directly extract information from rough data (no preprocessing)

- Many recent results validate the practical interest of the Machine Learning approach

- State-of-the-Art Template Attack separates resynchronization/dimensionality reduction from characterization

- Deep Learning provides an integrated approach to directly extract information from rough data (no preprocessing)

- Many recent results validate the practical interest of the Machine Learning approach

- We are in the very beginning and we are still discovering how much Deep Learning is efficient

- State-of-the-Art Template Attack separates resynchronization/dimensionality reduction from characterization

- Deep Learning provides an integrated approach to directly extract information from rough data (no preprocessing)

- Many recent results validate the practical interest of the Machine Learning approach

- We are in the very beginning and we are still discovering how much Deep Learning is efficient

- New needs:

- big data-bases for the training,

- platforms to enable comparisons and benchmarking,

- create an open community "ML for Embedded Security Analysis",

- encourage exchanges with the Machine Learning community,

- understand the efficiency of the current countermeasures

#### Conclusions

- State-of-the-Art Template Attack separates resynchronization/dimensionality reduction from characterization

- Deep Learning provides an integrated approach to directly extract information from rough data (no preprocessing)

- Many recent results validate the practical interest of the Machine Learning approach

- We are in the very beginning and we are still discovering how much Deep Learning is efficient

- New needs:

- big data-bases for the training,

- platforms to enable comparisons and benchmarking,

- create an open community "ML for Embedded Security Analysis",

- encourage exchanges with the Machine Learning community,

- understand the efficiency of the current countermeasures

#### Thank You!

#### Questions?

May, PHYSIC 2018 | E. Prouff | 23/23

#### FHE AND MPC PRIVACY PRESERVING COMPUTATIONS IN THE CLOUD

Nicolas Gama // EPFL

Slides sur http://lab.algonics.net/fc18/index-phisic.html

# Starting transition towards products embedding post-quantum cryptography

Yannick Teglia Aline Gouget

Phisic 2018 – Ecole des Mines de Saint-Etienne - Gardanne

Gemalto – Security Consulting & Services

# Outlook

- ×Quantum threat to today's cryptography

- × Theoretical resistance of current cryptographic algorithms

- × Quantum algorithms & quantum computers

- × Current status

- × Post-Quantum Cryptography

- × Running initiatives

- × Different families and noticeable characteristics

- × Foreseen consequences in current and coming products

- × Conclusion

2 | Starting transition towards products embedding post-quantum cryptography

### Quantum threat to today's cryptography

3 | Starting transition towards products embedding post-quantum cryptography

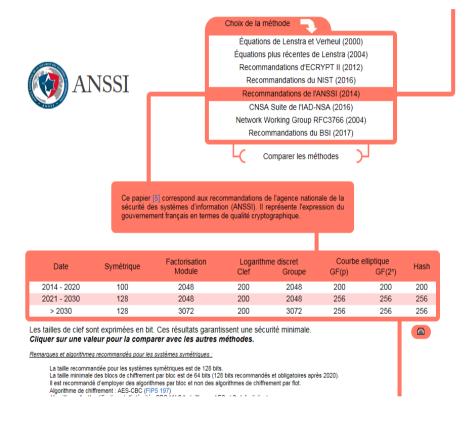

### **Theoretical Resistance of Cryptographic Algorithms**

- The resistance of a cryptographic algorithm is relative to the best known attack

- For Public Key cryptography, those attacks consist in solving the underlying mathematical « hard » problem

- × Factorization for RSA

- × The best known algorithm is sub exponential

- × Discrete logarithm for Elliptic curves

- × The best known algorithm is fully exponential

- For secret key cryptography, attacks are considered on a 'per case' basis

- For AES-128, the best known attack (Bogdanov et al. [1]) would require 2<sup>126.2</sup> operations instead of 2<sup>128</sup> for brute force

- × Advances are monitored by

- × Academia/industry (Lenstra et al [2], Ecrypt [3], ...)

- Governmental agencies (ANSSI[4], NIST[5], BSI[6])

- The keylength has then to be set accordingly to ensure the correct security level

- The industry has to comply to requested security levels

Starting transition towards products embedding post-quantum cryptography

www.keylenghth.com

# Quantum Algorithms for Cryptography

- In the middle 1990s, Grover [7] and Shor [8] published algorithms that could defeat some cryptographic primitives using a Quantum Computer

- × Shor

- × Specific use: factoring large integers and finding discrete logarithms

- × Cost reduced: from sub exponential to quadratic

- × Grover

- × Generic use: provides polynomial speed-up in unstructured search

- × Could be applied to symmetric cryptography

- × Cost reduced by a square root factor

- A Quantum Computer is expected to increase the computational power beyond the usual limits

- Quantum systems could be in multiple states at the same time

From sequential computation to « holistic computation » (Breton [14])

- Bringing together those algorithms and real Quantum Computers could then theoretically jeopardize today's cryptography

5 | Starting transition towards products embedding post-quantum cryptography

### Threats on current cryptography: where do we stand?

- × Symmetric Cryptography

- × AES-256 secure beyond 2050 (ETSI [15])

- × AES-128, possibly secure yet

- × 2<sup>81</sup> operations expected instead of the 2<sup>64</sup> predicted by the rule of thumb (GrassI [17])

- $\,\times\,\,$  The cost of the algorithm as to be taken into account as well

- × 3-DES with 3 keys

- × No academic publication

- × NIST says that 3-DES with 3 keys is ok up to 2030

- × Several MAC and authenticated encryption modes can be broken (Kaplan [18])

- × Hash Functions

- × SHA-256 secure beyond 2050 (ETSI [15])

- × Attacks in  $2^{166}$  for SHA-2 and SHA-3 (instead of  $2^{128}$ )

- × Hash based signatures scheme safe against quantum computing

- × ECC and RSA

- × A Post Quantum RSA would require a 1 TB key from 4kbit primes (Bernstein [26])

- × Replacement is needed for "long term" ⇔ when quantum computers are available

- No short-term endorsement of PQ cryptosystems in RGS Annex B1 of ANSSI (Gilbert [40])

- × Potential exception for hash-based signatures

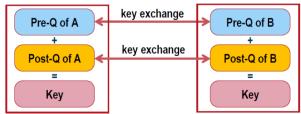

- $\,\times\,\,$  Hybrid systems combining pre-quantum and post-quantum likely to be endorsed

6 | Starting transition towards products embedding post-quantum cryptography

# Current Quantum Computers ...

- × The real computationnel power of a quantum computer is difficult to estimate

- × The qubit could be seen as a metric to quantify the power of a Quantum Computer

- × 1998 2 qubits

- × ...

- × 2018 72 qubits

- × NB: D-wave is claiming 128 qubits but with a different architecture and a limited scope

- × Several recent annoucements regarding Quantum Computers

- × Intel Tangle Lake : 49 qubit

- × IBM Q: 50 qubit

- × Google Bristlecone: 72 qubit

- × Different technologies and architectures

- × There are qubits and qubits

- × Silicon qubits (Intel) vs regular qubits

- × Universal Quantum Computers vs dedicated quantum annealing (D-Wave)

- × The latter cannot process Shor's algorithm

### ... And their limits

- × Regarding factorization, quantum computers are currently only able to factor 15

- × Quantum Computing is a huge engineering challenge

- × Nanotechnlogy, quantum electronics, ...

- × Quantum computers are not yet to replace classical ones

- × Bob Sutor, VP of IBM Q Strategy & Ecosystem [16]:

And if you're waiting for today's quantum computers to be able to compete with modern supercomputers anytime soon, you shouldn't hold your breath. "We need to get several orders of magnitude better than we are now to probably move into that period where we're solving the really super hard problems," he said.

- Some people even think that it cannot ever be reached, as mathematician Gil Kalai [9] recently mentionned:

- × Quantum computing is like any similar process in nature noisy, with random fluctuations and errors. [...]

- \* « We need what's known as quantum error correction [...] the amount of noise has to go below a certain level, or threshold. »

- × « [...] our first result shows that the noise level cannot be reduced, because doing so will contradict an insight from the theory of computing »

- × « So I don't need to be certain, I can simply wait and see. »

- 8 | Starting transition towards products embedding post-quantum cryptography

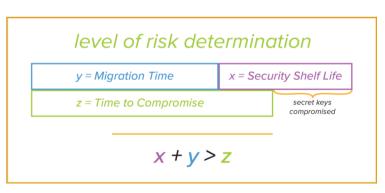

# **Current status & Emergency Level**

### THE SKY IS FALLING?

• If a large-scale quantum computer could be built then....

### The sky is falling?

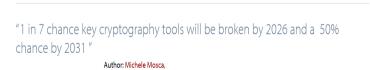

When will a quantum computer be built that breaks current crypto?

15 years, \$1 billion USD, nuclear power plant (to break RSA-2048) (PQCrypto 2014, Matteo Mariantoni)

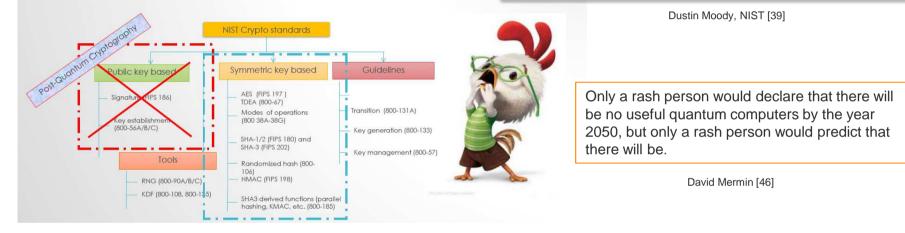

Dustin Moody, NIST [10]

Institute for Quantum Computing & Special Advisor on Cyber Security to the Global Risk Institute

Mosca Theorem, source Medium [19]

9 | Starting transition towards products embedding post-quantum cryptography

# Running Initatives for Post Quantum Cryptography

## NSA annoucement & NIST call for submissions

- Back in august 2015, NSA explicitly talked about the threat of quantum computers

- "Unfortunately, the growth of elliptic curve use has bumped up against the fact of continued progress in the research on quantum computing, necessitating a re-evaluation of our cryptographic strategy."

- "we recommend not making a significant expenditure to [make the transition to Suite B] at this point but instead to prepare for the upcoming quantum resistant algorithm transition."

- × In 2016: announcement of NIST's call for submissions on postquantum public-key cryptography

- × <u>NB:</u> Post-Quantum Cryptography is not Quantum Cryptography

- × Quantum Cryptography, Bennett and Brassard [45]

- × Use quantum mechanics to perform cryptographic operations

- × Post-Quantum Cryptography

- × Process quantum resistant cryptographic algorithms on regular devices

#### Timeline

\*This is a tentative timeline, provided for information, and subject to change.

#### Date

| <         | Feb 24-26, 2016            | NIST Presentation at PQCrypto 2016: Announcement and outline of NIST's Call for Submissions (Fall 2016),<br>Dustin Moody |

|-----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

|           | April 28, 2016             | NIST releases NISTIR 8105, Report on Post-Quantum Cryptography                                                           |

|           | Dec 20, 2016               | Formal Call for Proposals                                                                                                |

|           | Nov 30, 2017               | Deadline for submissions                                                                                                 |

|           | Dec 4, 2017                | NIST Presentation at AsiaCrypt 2017: The Ship Has Sailed: The NIST Post-Quantum Crypto "Competition",<br>Dustin Moody    |

|           | Dec 21, 2017               | Round 1 algorithms announced (69 submissions accepted as "complete and proper"                                           |

|           | Apr 11, 2018               | NIST Presentation at PQCrypto 2018: Let's Get Ready to Rumble - The NIST PQC "Competition", Dustin<br>Moody              |

| $\langle$ | April 11-13, 2018          | First PQC Standardization Conference - Submitter's Presentations                                                         |

|           | 2018/2019                  | Round 2 begins                                                                                                           |

| 6         | August 2019<br>(tentative) | Second PQC Standardization Conference                                                                                    |

|           | 2020/2021                  | Round 3 begins or select algorithms                                                                                      |

| $\langle$ | 2022/2024                  | Draft Standards Available                                                                                                |

|           |                            | csrc.nist.gov [37]                                                                                                       |

## Other initiatives: examples

gemalto

### Candidates Families for Post Quantum Cryptography

- × Error Correcting Codes Cryptography

- × With Goppa codes

- × 1978, Mc Eliece [20]

- × Public keys for from 0.5 up to 1Mbyte

- × Slow key generation

- × With more structured codes (QC-MDPC)

- × Smaller Public Keys

- × Structure of code could lead to vulnerabilities

- × (Small) decryption error probability

- × Hash Based Signatures

- × 1979, Lamport [25]

- × Recent proposals like SPHINCS (signatures of 41kbytes) or XMSS (signatures of 1-5 kbytes)

- × Multivariate Cryptography

- × 1996, Patarin [23]

- × Large public keys (27.9 to 75 kbytes)

- × Lattice Based Cryptography

- × 1996, Ajtai [21] and Regev [22]

- × NTRU, Keyber, Newhope, Frodo, ...

- × Well suited for ephemeral key exchange [41]

- × Pretty fast (equivalent to ECDH) on Cortex M4 [42] and Intel [41]

- × Isogeny Based Key Exchange

- × 2006, Rostovtsev [24]

- × New field of research

- × Relatively slow

### Candidates Families for Post Quantum Cryptography

| Scheme                                                                                 |             | Public key size<br>(bytes) | Data size<br>(bytes)    |

|----------------------------------------------------------------------------------------|-------------|----------------------------|-------------------------|

| Public-key signatures:                                                                 |             |                            |                         |

| <ul> <li>Hash based:</li> <li>XMSS (stateful)</li> <li>SPHINCS (state free)</li> </ul> | [17]<br>[9] | 64<br>1,056                | 2,500 – 2,820<br>41,000 |

| <ul> <li>Multivariate based:</li> <li>– HFEv-*</li> </ul>                              | [51]        | 500,000 - 1,000,000        | 25 - 32                 |

| Public-key encryption:                                                                 | (           |                            |                         |

| <ul> <li>Code based:</li> <li>McEliece</li> </ul>                                      | [10]        | 958,482 - 1,046,739        | 187 - 194               |

| <ul> <li>Lattice based:</li> <li>NTRUEncrypt</li> </ul>                                | [35, 37]    | 1,495 – 2,062              | 1,495 – 2,062           |

| Key exchange:                                                                          |             |                            |                         |

| <ul> <li>Lattice based:</li> <li>NewHope</li> </ul>                                    | [3]         |                            | 1,824 – 2,048           |

| <ul> <li>Supersingular isogenies:</li> <li>SIDH</li> </ul>                             | [21]        | _                          | 564                     |

| Classical schemes:                                                                     |             |                            |                         |

| <ul> <li>RSA:</li> <li>– RSA-2048</li> <li>– RSA-4096</li> </ul>                       |             | 256<br>512                 | 256<br>512              |

| <ul> <li>ECC:</li> <li>256-bit</li> <li>512-bit</li> </ul>                             |             | 32                         | 32<br>64                |

| <ul> <li>Key exchange:</li> <li>DH</li> </ul>                                          |             | 64                         | 256 - 512               |

| – ECDH                                                                                 |             | _                          | 32 – 64                 |

- × Noticeable Characteristics

- × Usually (much) bigger keys

- × Expected longer execution time with respect to current cryptography

- × Heterogeneous arithmetic/algorithmic solutions

- × Depends on family/refinement/targeted application

Source Fraunhofer [27]

## Consequences on implementations - Functionnalities - Security

## Business as usual ?

- × Post-Quantum crypto primitives will be run on classical electronic devices able to manage

- × Higher key size

- × Increased computationnal capabilities

- × Gaussian sampling capabilities (for lattice based crypto)

- × Functionnalities requirements

- × Increased memory footprint and/or gate-count

- × Code Size

- × Key storage

- × Additional cryptographic engines or use of existing capabilities?

- × Dedicated Random Number Generators ?

- × Providing gaussian variables instead of usual uniform ones

- × Some attacks have already been published for every 'old' family of PQ Cryptosystems

- Timing Attacks (Strentzke et al. [28], [29], [31]) and SPA (Molter et al. [30], Heyse et al. [32]) on Mc Eliece

- × Timing Attack on NTRU (Silverman et al. [33])

- Side Channel Attacks (Primas et al. [34]) and Fault Injection(Espitau et al. [35],[36]) on latticebased schemes

- × Side Channel Attacks on Hash Based Signatures (Eisenbarth et al. [44])

- × Security

- × Usual devices will leak in the usual way if no counter measure is applied

- × Possible new weaknesses / new ways for attacking

## What's next in term of actual attacks?

- × Well, I don't know ...

- × Try to take advantage of long processing and big keys + algebraic structures / arithmetic patterns

- × Will PQ Cryptosystems be the flagship for Machine Learning: on the tracks of RSA and ECC ?

- × Time/Frequency analysis to look for patterns

- × Fault Injection to take advantage of the increased surface

- × Would data be the favorite target (as for symmetric key crypto but also RSA)?

- × Or rather treatments that reveals data (as for RSA and ECC) ?

- More complex software stacks that will have to deal with pre quantum and post quantum schemes (crypto agility)

- × The overall probability of a bug is increased

- × The attack surface is enlarged for fault injection and software attacks

- × Gaussian TRNG

- × Usual (i.e. uniform) TRNG have not been widely attacked while being at the bosom of the security protocols

- × Gaussian TRNG are important for lattice based cryptography; they can then be a preferred target

- × Are gaussian TRNG more easily attackable than regular ones?

- × Successful attacks can turn into a generic trend, back to uniform TRNG targeting 'pre-quantum' cryptosystems

- × Quantum computers are likely to boost machine learning, yielding advances in cryptanalysis ([38])

## What is needed?

- × Further studies !

- × Assess security of NIST candidates

- × Theoretical standpoint

- × With respect to side channel attacks and fault injection

- × Primitives to to efficiently & securely implement Post-Quantum schemes

- × Keep and adapt current crypto engines?

- × Develop brand new ones?

- × Ways to ensure proper & secure transition within products

- × Secure crypto agility required

- × Are current firmware upgrade mechanims enough?

- × Post-Quantum Cryptography in Gemalto

- × Follow up on theoretical and practical advances in the field

- × Involved in collaborative project RISQ

- × Several Proof of Concept running in Gemalto

- × Gemalto to work on the subject through additionnal collaborative projects

- × Theoretical resistance study

- × Side Channel and Fault Injection resistance

- × Need for additionnal cryptographic bricks

- × Random Sampling capabilities

## Take Away

- × Quantum Computers are not there yet

- × Engineering problem to solve

- × Theoretical problems may also occur on the road

- × But Post Quantum Cryptography would be needed at some point

- × AES-256, SHA-256 seems safe

- × ECC and RSA are in danger

- × Probably moving in different steps as suggested by Shamir [43], depending on the maturity level

- × Production schemes (Hash Hased)

- × Development schemes (Lattice, Code Based, Multivariate)

- × Research schemes (Isogenies)

- × Several proposals to emerge from the NIST initiative by 2024

- × The robustness of those constructions have to be evaluated

- × Side Channel / Fault Injection

- × Software Attacks / Logical Attacks

- × Provisionning needs to be defined

- × Additionnal arithmetic/algorithmic core bricks

- × Gaussian RNG

- × Counter measures for Side Channel Attacks and Fault Injection

- × Crypto agility capabilities to manage the transition

### References

- × [1] Andrey Bogdanov; Dmitry Khovratovich & Christian Rechberger (2011). "Biclique Cryptanalysis of the Full AES«

- × [2] Selecting Cryptographic Key Sizes, Arjen K. Lenstra and Eric R. Verheul, Journal Of Cryptology, vol. 14, p. 255-293, 2001.

- × [3] Yearly Report on Algorithms and Keysizes (2012), D.SPA.20 Rev. 1.0, ICT-2007-216676 ECRYPT II, 09/2012.

- × [4] Mécanismes cryptographiques Règles et recommandations, Rev. 2.03, ANSSI , 02/2014.

- × [5] Recommendation for Key Management, Special Publication 800-57 Part 1 Rev. 4, NIST, 01/2016.

- × [6] Kryptographische Verfahren: Empfehlungen und Schlüssellängen, TR-02102-1 v2017-01, BSI, 02/2017.

- [7] Grover L.K. : A fast quantum mechanical algorithm for database search, Proceedings, 28th Annual ACM Symposium on the Theory of Computing, (May 1996) p. 212

- × [8] Peter W. Shor: Polynominal time algorithms for discrete logarithms and factoring on a quantum computer. ANTS 1994: 289

- × [9] The Argument Against Quantum Computers, <u>https://www.quantamagazine.org/gil-kalais-argument-against-quantum-computers-</u>20180207/

- × [10] THE SHIP HAS SAILED, The NIST Post-Quantum Crypto "Competition", Dustin Moody, NIST

- × [11] A. Hülsing, D. Butin, S.-L. Gazdag, and A. Mohaisen. XMSS: Extended Hash-based Signatures, July 2017. Work in Progress –

- × [12] Physical Attack Vulnerability of Hash-Based Signature Schemes, Master-Thesis von Matthias Julius Kannwischer, 2017

- × [13] Stefan Heyse. "Low-Reiter: Niederreiter encryption scheme for embedded microcontrollers." Pages 165–181 in: Nicolas Sendrier (editor). Post-Quantum Cryptography, Third international workshop, PQCrypto 2010. Lecture Notes in Computer Science 6061

- × [14] Aurons-nous un jour des ordinateurs quantiques ?, <u>https://www.franceculture.fr/emissions/la-conversation-scientifique/aurons-nous-un-jour-des-ordinateurs-quantiques</u>

- × [15] ETSI GR QSC 006 V1.1.1 (2017-02)

- × [16] Not even IBM is sure where its quantum computer experiments will lead, <u>https://www.engadget.com/2018/02/23/ibm-q-quantum-computer-experiments/</u>

- × [17] Markus Grassl, Brandon Langenberg, Martin Roetteler, Rainer Steinwandt: Applying Grover's Algorithm to AES: Quantum Resource Estimates. PQCrypto 2016: 29-43

- × [18] Marc Kaplan, Gaëtan Leurent, Anthony Leverrier, María Naya-Plasencia: Breaking Symmetric Cryptosystems Using Quantum Period Finding. CRYPTO (2) 2016: 207-237

- × [19] When Should You Start Worrying About Post-Quantum Cryptography?, <u>https://medium.com/@EncryptKen/when-should-you-start-worrying-about-post-quantum-cryptography-c881102c3f73</u>

- [20] Robert J. McEliece, « A Public-Key Cryptosystem Based on Algebraic Coding Theory », Jet Propulsion Laboratory DSN Progress Report,? 1978, p. 42–44

### References

- × [21] Mikiós Ajtai, « Generating hard instances of lattice problems », Symposium on Theory of Computing, 1996

- × [22] Oded Regev, « On lattices, learning with errors, random linear codes, and cryptography », Symposium on Theory of Computing, 2005

- × [23] Patarin, J. Hidden fields equations (HFE) and isomorphisms of polynomials (IP): two new families of asymmetric algorithms. In Maurer, U. M. (ed.) Advances in Cryptology EUROCRYPT '96

- × [24] Alexander Rostovtsev et Anton Stolbunov, « Public-Key Cryptosystem based on Isogenies », iacr ePrint Reports, 2006

- × [25] Lamport, L. Constructing digital signatures from a one way function. Technical Report SRI-CSL-98, SRI International Computer Science Laboratory (1979)

- × [26] Daniel J. Bernstein, Nadia Heninger, Paul Lou et Luke Valenta, « Post-quantum RSA », Post-Quantum Cryptography, Springer, Cham, série Lecture Notes in Computer Science,? 26 juin 2017, p. 311–329

- × [27] White Paper Practical PostQuantum Cryptography August 18, 2017 Dr. Ruben Niederhagen Department CyberPhysical Systems Security (CSS) Prof. Dr. Michael Waidner Director Fraunhofer SIT and Professor for Security in IT at TU Darmstadt Fraunhofer Institute for Secure Information Technology SIT

- × [28] Falko Strenzke, Erik Tews, H. Gregor Molter, Raphael Overbeck, Abdulhadi Shoufan: Side Channels in the McEliece PKC. PQCrypto 2008: 216-229

- × [29] Falko Strenzke: A Timing Attack against the Secret Permutation in the McEliece PKC. PQCrypto 2010: 95-107

- [30] H. Gregor Molter, Marc Stöttinger, Abdulhadi Shoufan, Falko Strenzke: A simple power analysis attack on a McEliece cryptoprocessor. J. Cryptographic Engineering 1(1): 29-36 (2011)

- × [31] Falko Strenzke: Timing Attacks against the Syndrome Inversion in Code-Based Cryptosystems. PQCrypto 2013: 217-230